L: Wafer-level reliability testing Model 4200A-SCS Parameter Analyzer

L-4 4200A-901-01 Rev. C / February 2017

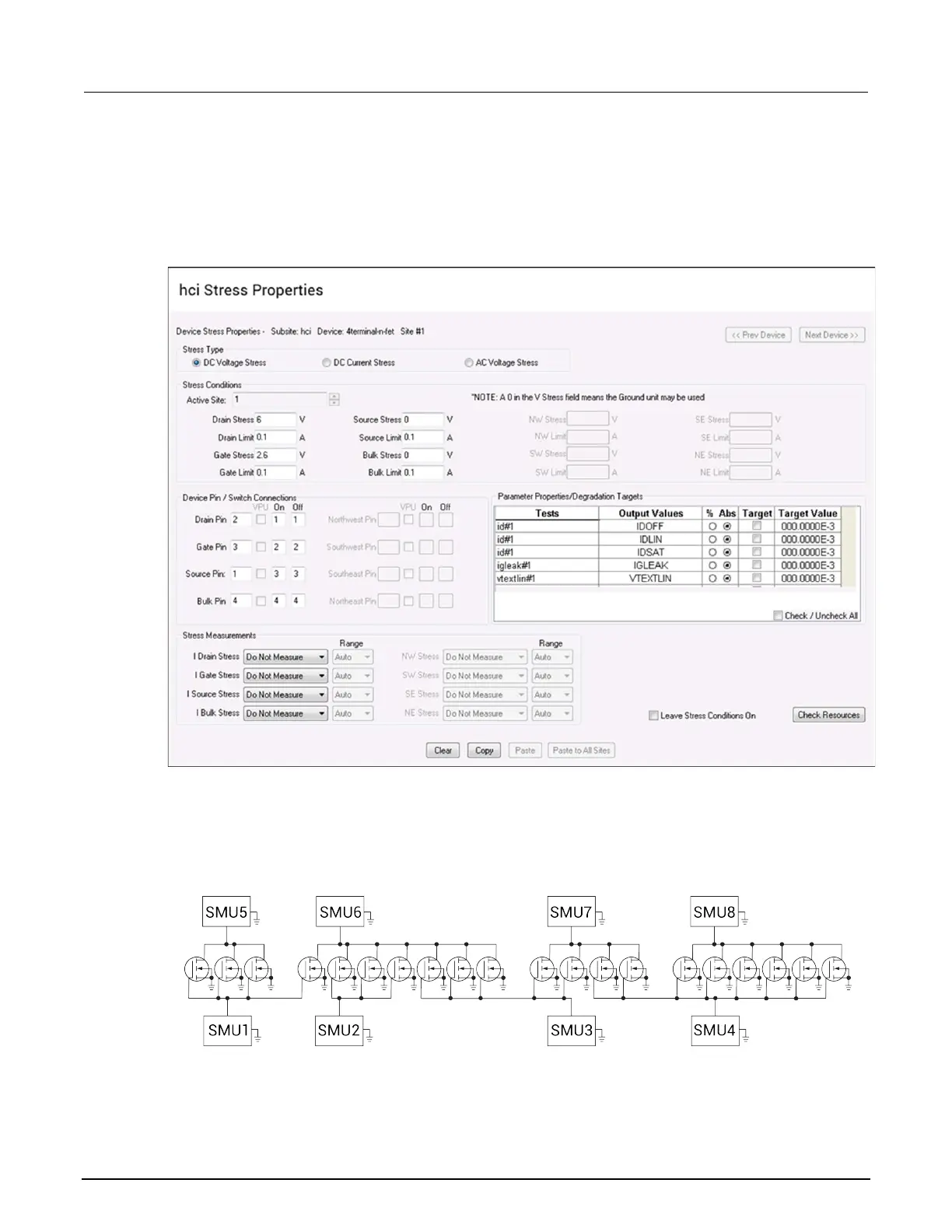

For the hci-1-dut project, the hci subsite is set up for subsite cycling using voltage stressing on

the single n-channel MOSFET device (4terminal-n-fet). After the first pre-stress cycle to perform

characterization tests, subsequent cycles voltage stress the device for a specified time before

repeating the tests. The Stress Properties pane for the hci-1-dut project is shown in the following

figure.

Figure 829: Stress Properties for the hci-1-dut project

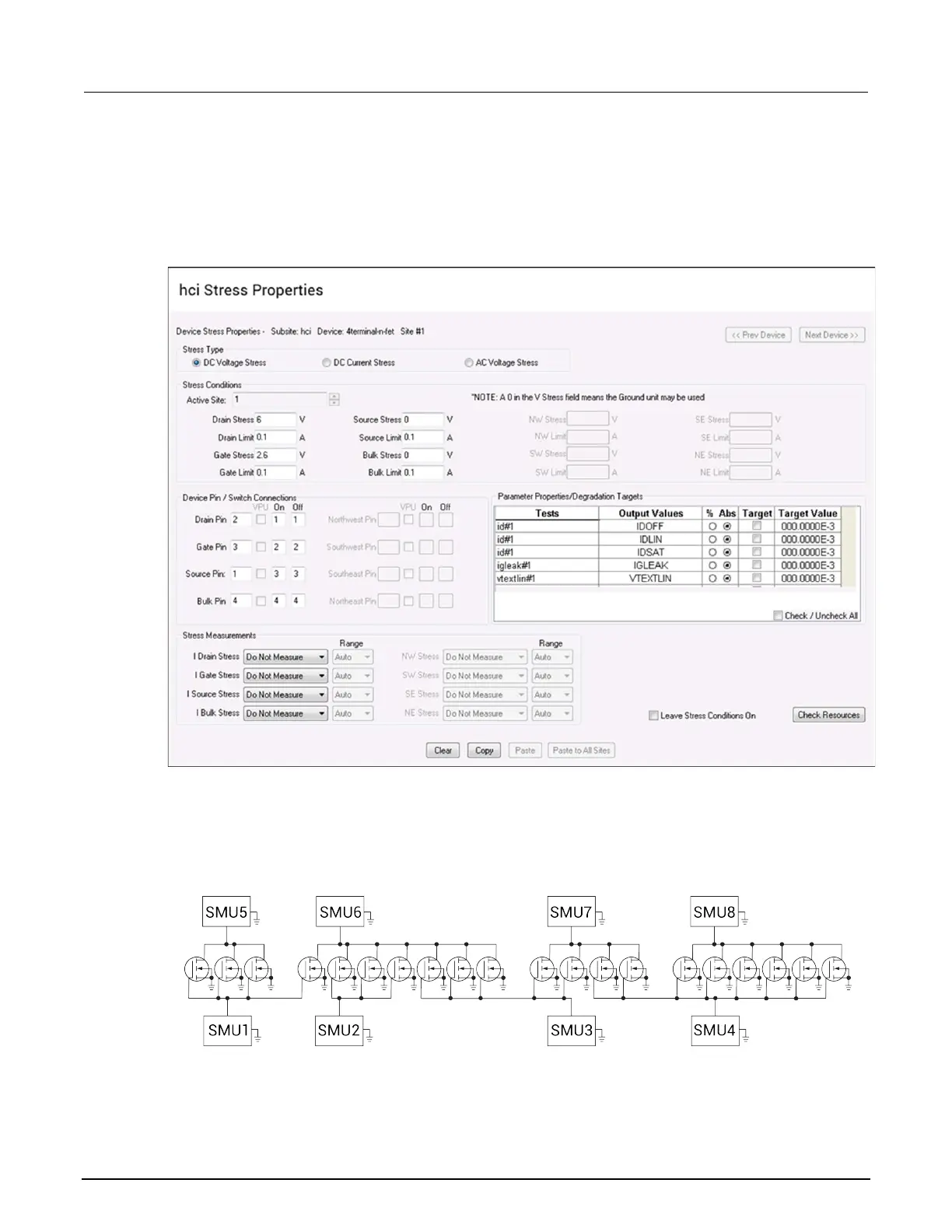

The hci-4-dut project is similar to the hci-1-dut project except that it is configured to test four

devices using a switching matrix for connections.

In a parallel connection scheme, up to 20 devices can be stressed by voltage. The figure below

shows an example of 20 parallel-connected devices being stressed by eight gate and drain voltages.

Figure 830: HCI and NBTI tests: 20 parallel-connected devices stressed by voltage

Loading...

Loading...