MIPS R4000 Microprocessor User's Manual 89

Memory Management

EntryHi Register (CP0 Register 10)

The EntryHi register holds the high-order bits of a TLB entry for TLB read

and write operations.

The EntryHi register is accessed by the TLB Probe, TLB Write Random,

TLB Write Indexed, and TLB Read Indexed instructions.

Figure 4-9 shows the format of this register.

When either a TLB refill, TLB invalid, or TLB modified exception occurs,

the EntryHi register is loaded with the virtual page number (VPN2) and

the ASID of the virtual address that did not have a matching TLB entry.

(See Chapter 5 for more information about these exceptions.)

Processor Revision Identifier (PRId) Register (15)

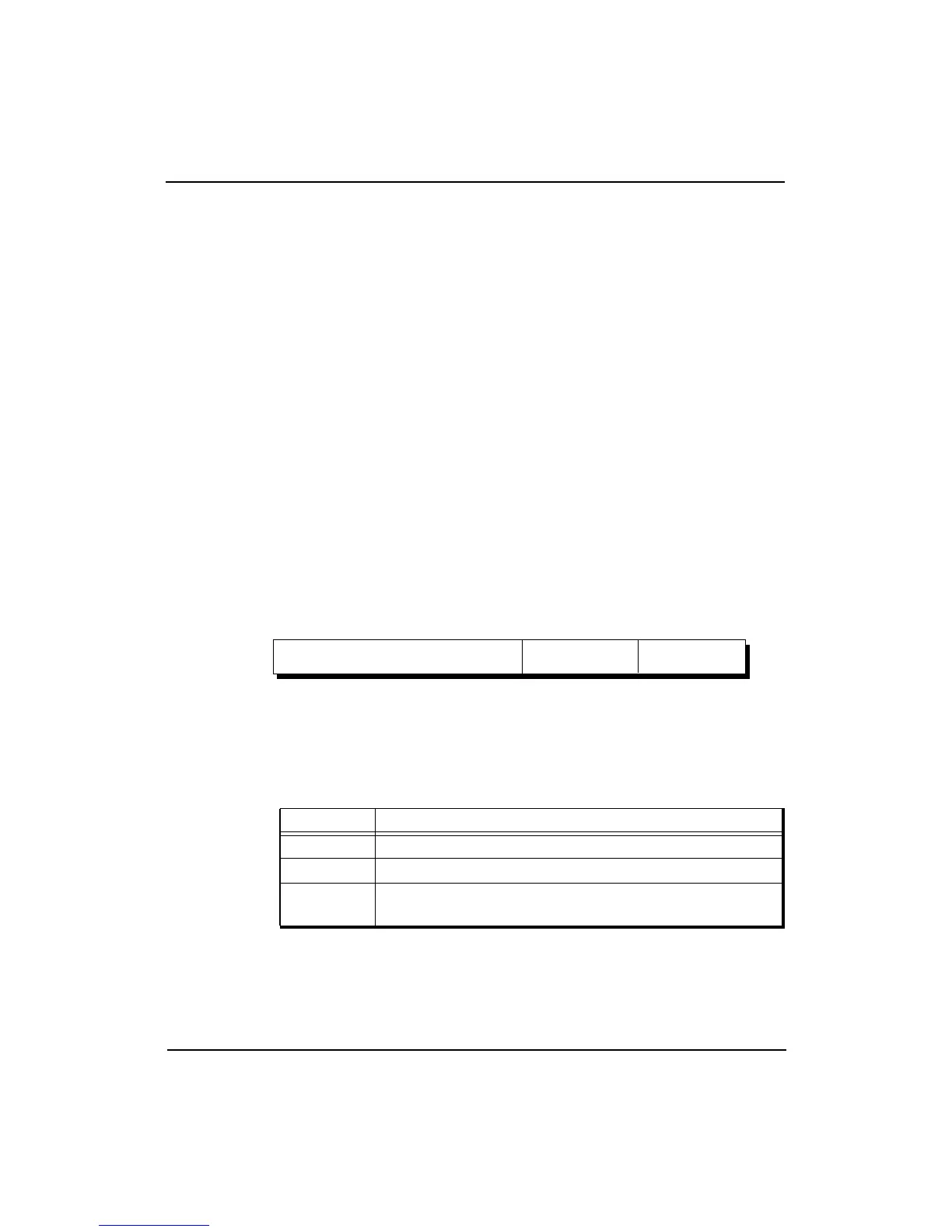

The 32-bit, read-only Processor Revision Identifier (PRId) register contains

information identifying the implementation and revision level of the CPU

and CP0. Figure 4-15 shows the format of the PRId register; Table 4-11

describes the PRId register fields.

Figure 4-15 Processor Revision Identifier Register Format

Table 4-11 PRId Register Fields

Field Description

Imp Implementation number

Rev Revision number

0

Reserved. Must be written as zeroes, and returns zeroes

when read.

16 15

PRId Register

31 0

16

Imp

88

0

8

Rev

7

Loading...

Loading...