MIPS R4000 Microprocessor User's Manual 113

CPU Exception Processing

WatchLo (18) and WatchHi (19) Registers

R4000 processors provide a debugging feature to detect references to a

selected physical address; load and store operations to the location

specified by the WatchLo and WatchHi registers cause a Watch exception

(described later in this chapter).

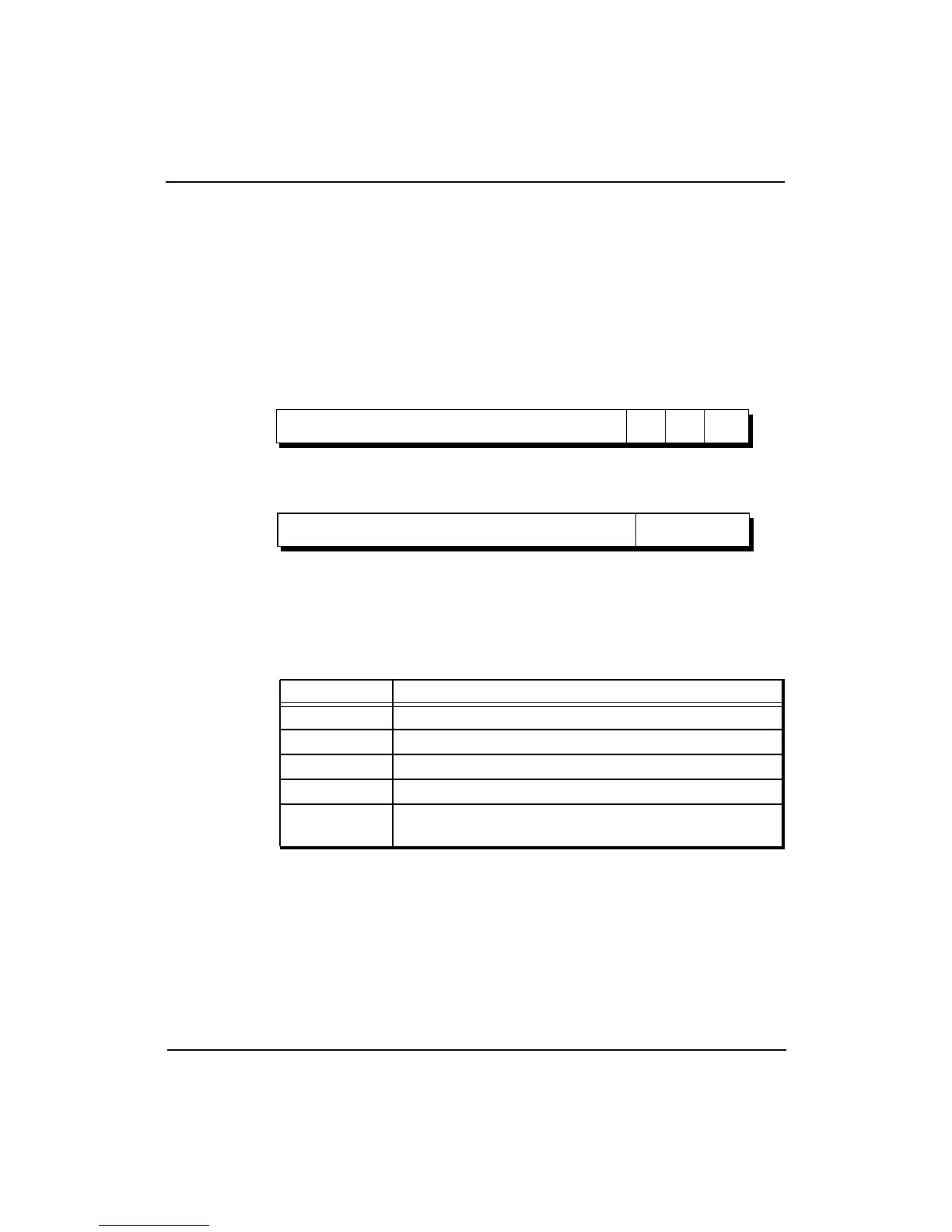

Figure 5-9 shows the format of the WatchLo and WatchHi registers;

Table 5-7 describes the WatchLo and WatchHi register fields.

Figure 5-9 WatchLo and WatchHi Register Formats

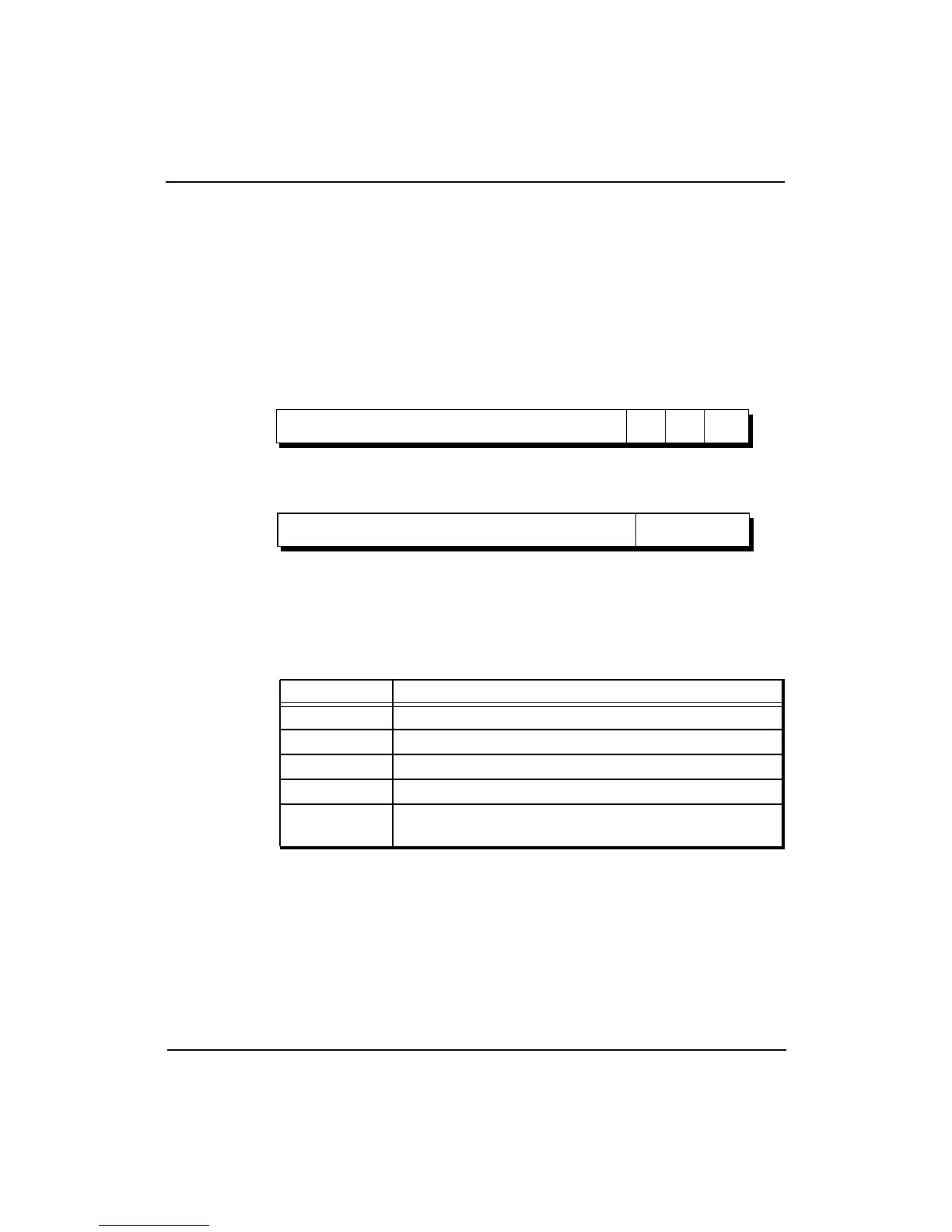

Table 5-7 WatchHi and WatchLo Register Fields

Field Description

PAddr1 Bits 35:32 of the physical address

PAddr0 Bits 31:3 of the physical address

R Trap on load references if set to 1

W Trap on store references if set to 1

0

Reserved. Must be written as zeroes, and returns

zeroes when read.

WatchLo Register

31

29 1

R WPAddr0

11

301

WatchHi Register

2

31

28 4

403

0 PAddr1

0

Loading...

Loading...