MIPS R4000 Microprocessor User's Manual 123

CPU Exception Processing

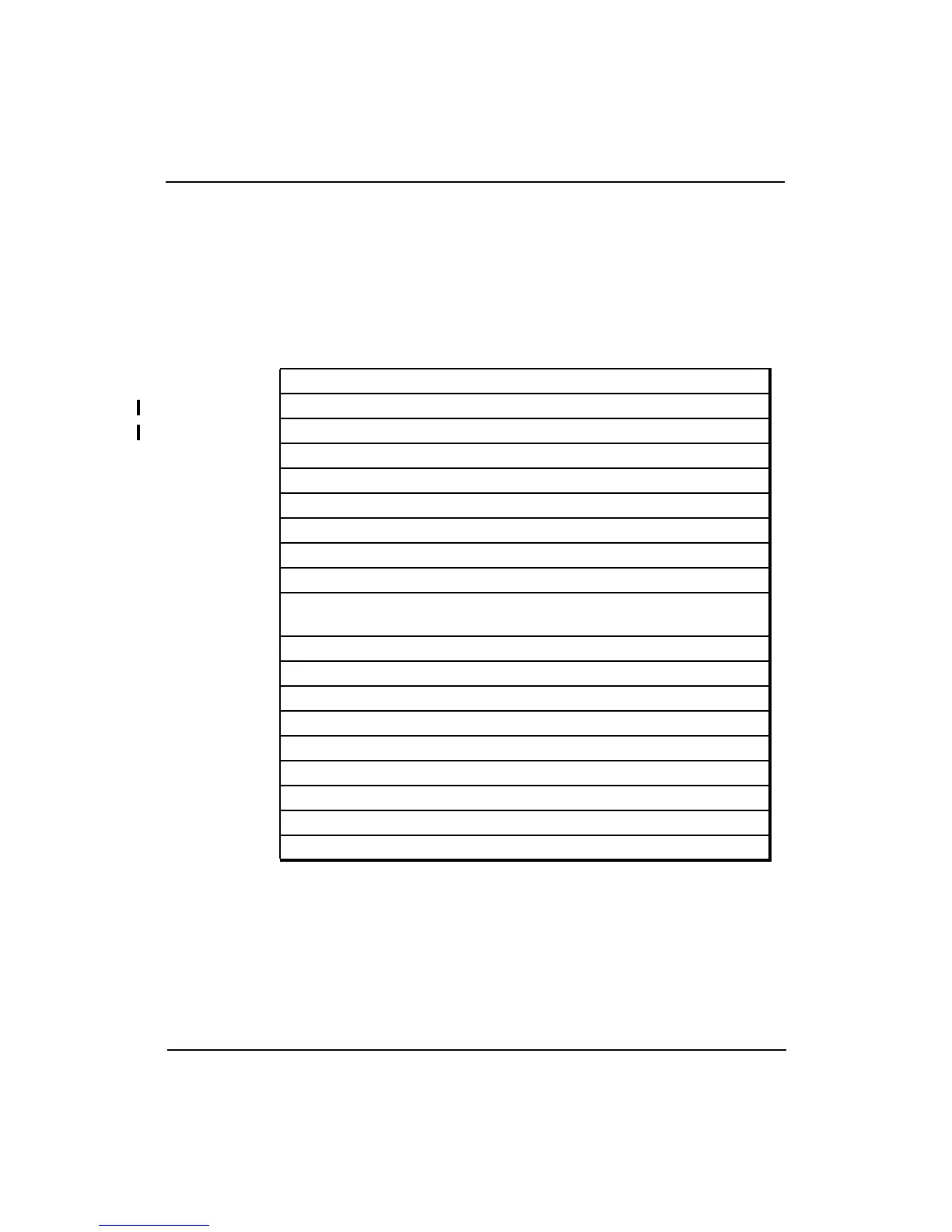

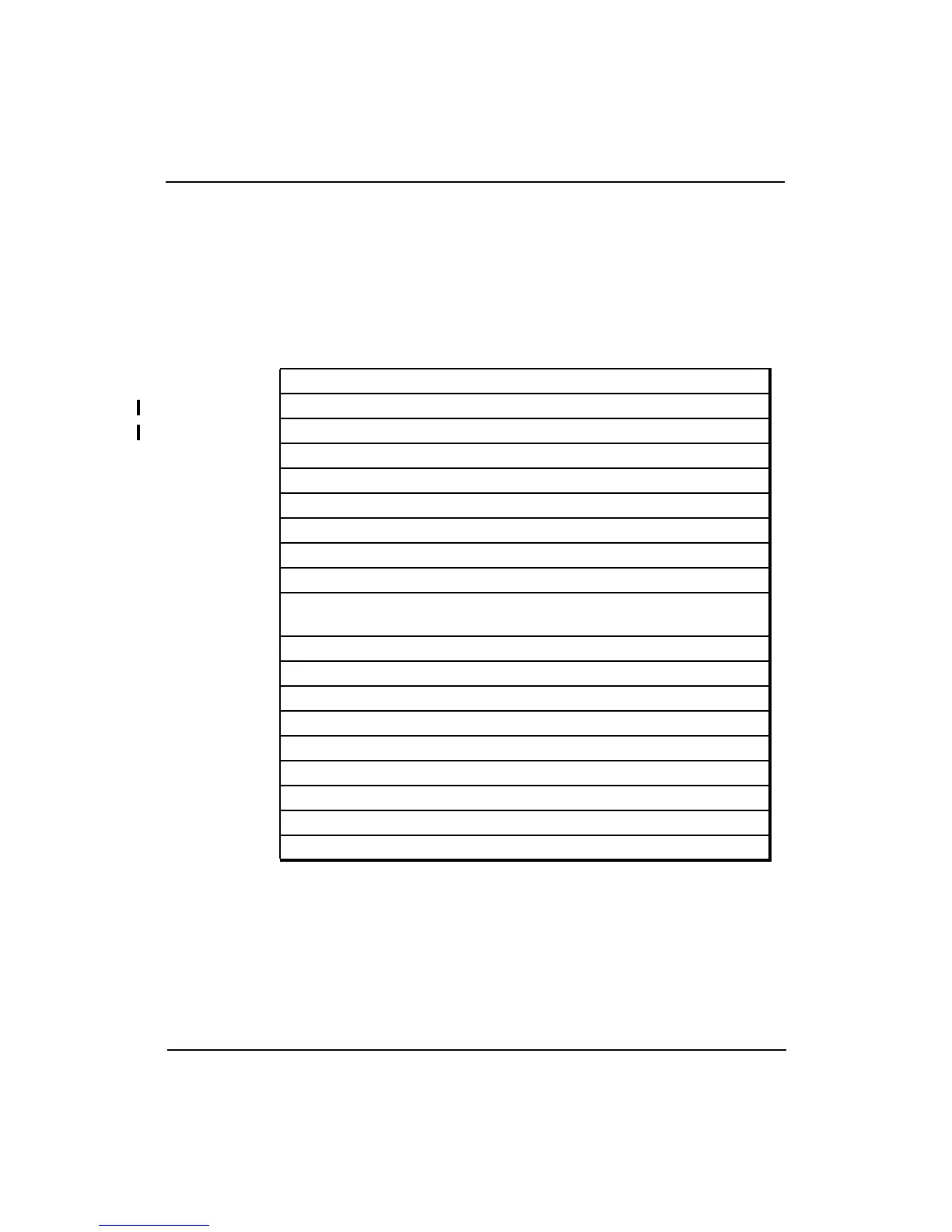

Priority of Exceptions

The remainder of this chapter describes exceptions in the order of their

priority shown in Table 5-13 with (certain of the exceptions, such as the

TLB exceptions and Instruction/Data exceptions, grouped together for

convenience). While more than one exception can occur for a single

instruction, only the exception with the highest priority is reported.

Table 5-13 Exception Priority Order

Generally speaking, the exceptions described in the following sections are

handled (“processed”) by hardware; these exceptions are then serviced by

software.

Reset (highest priority)

Soft Reset caused by Reset* signal

Nonmaskable Interrupt (NMI) (Soft Reset exception caused by NMI)

Address error –– Instruction fetch

TLB refill –– Instruction fetch

TLB invalid –– Instruction fetch

Cache error –– Instruction fetch

Virtual Coherency –– Instruction fetch

Bus error –– Instruction fetch

Integer overflow, Trap, System Call, Breakpoint, Reserved

Instruction, Coprocessor Unusable, or Floating-Point Exception

Address error –– Data access

TLB refill –– Data access

TLB invalid –– Data access

TLB modified –– Data write

Cache error –– Data access

Watch

Virtual Coherency –– Data access

Bus error –– Data access

Interrupt (lowest priority)

Loading...

Loading...