Chapter 3

48 MIPS R4000 Microprocessor User's Manual

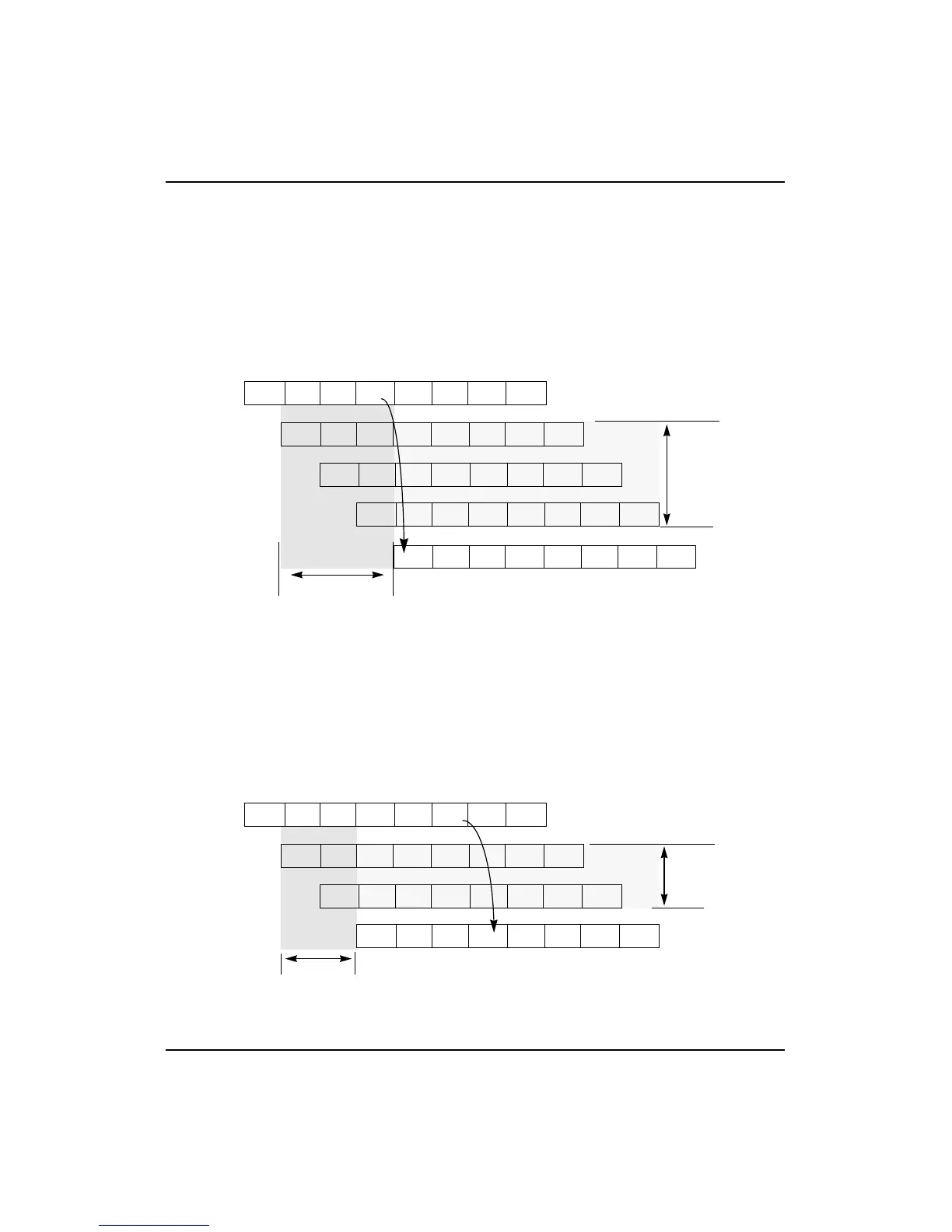

3.3 Branch Delay

The CPU pipeline has a branch delay of three cycles and a load delay of

two cycles. The three-cycle branch delay is a result of the branch

comparison logic operating during the EX pipeline stage of the branch,

producing an instruction address that is available in the IF stage, four

instructions later.

Figure 3-3 illustrates the branch delay.

Figure 3-3 CPU Pipeline Branch Delay

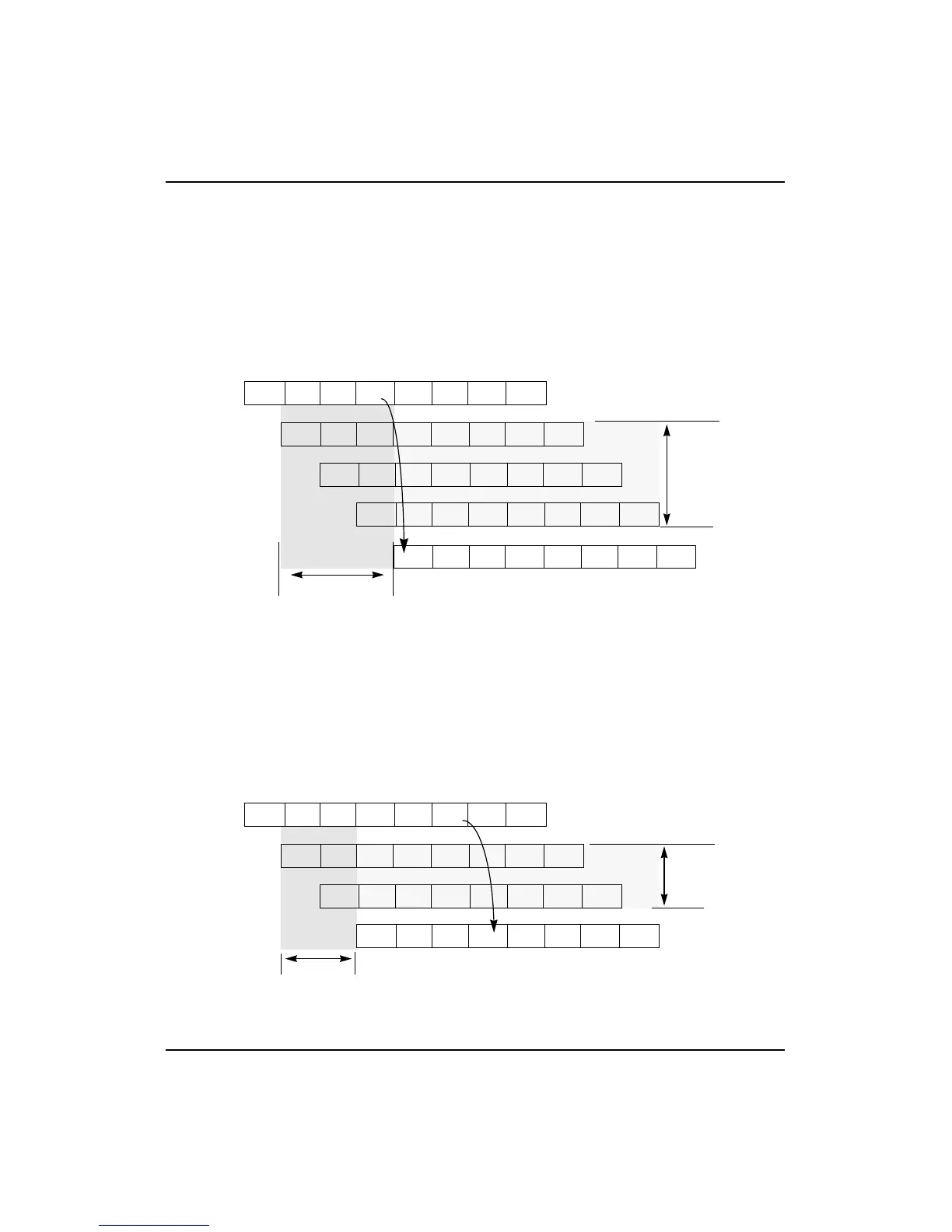

3.4 Load Delay

The completion of a load at the end of the DS pipeline stage produces an

operand that is available for the EX pipeline stage of the third subsequent

instruction.

Figure 3-4 shows the load delay of two pipeline stages.

Figure 3-4 CPU Pipeline Load Delay

branch

target

Branch Delay

three branch

delay

instructions

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

IF IS RF EX DF DS TC WB

load

f(load)

Load

two load

delay

instructions

Delay

Loading...

Loading...