MIPS R4000 Microprocessor User's Manual 359

System Interface

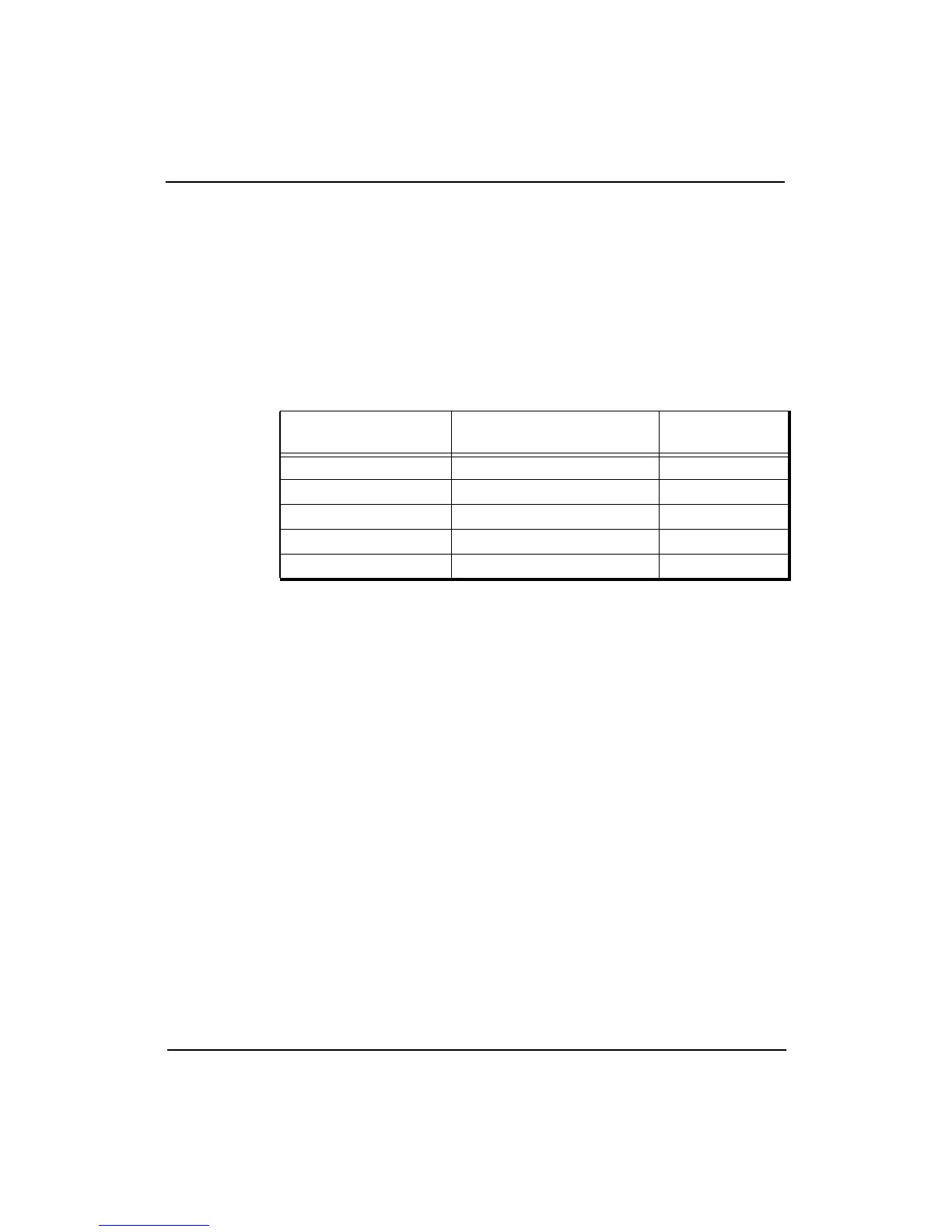

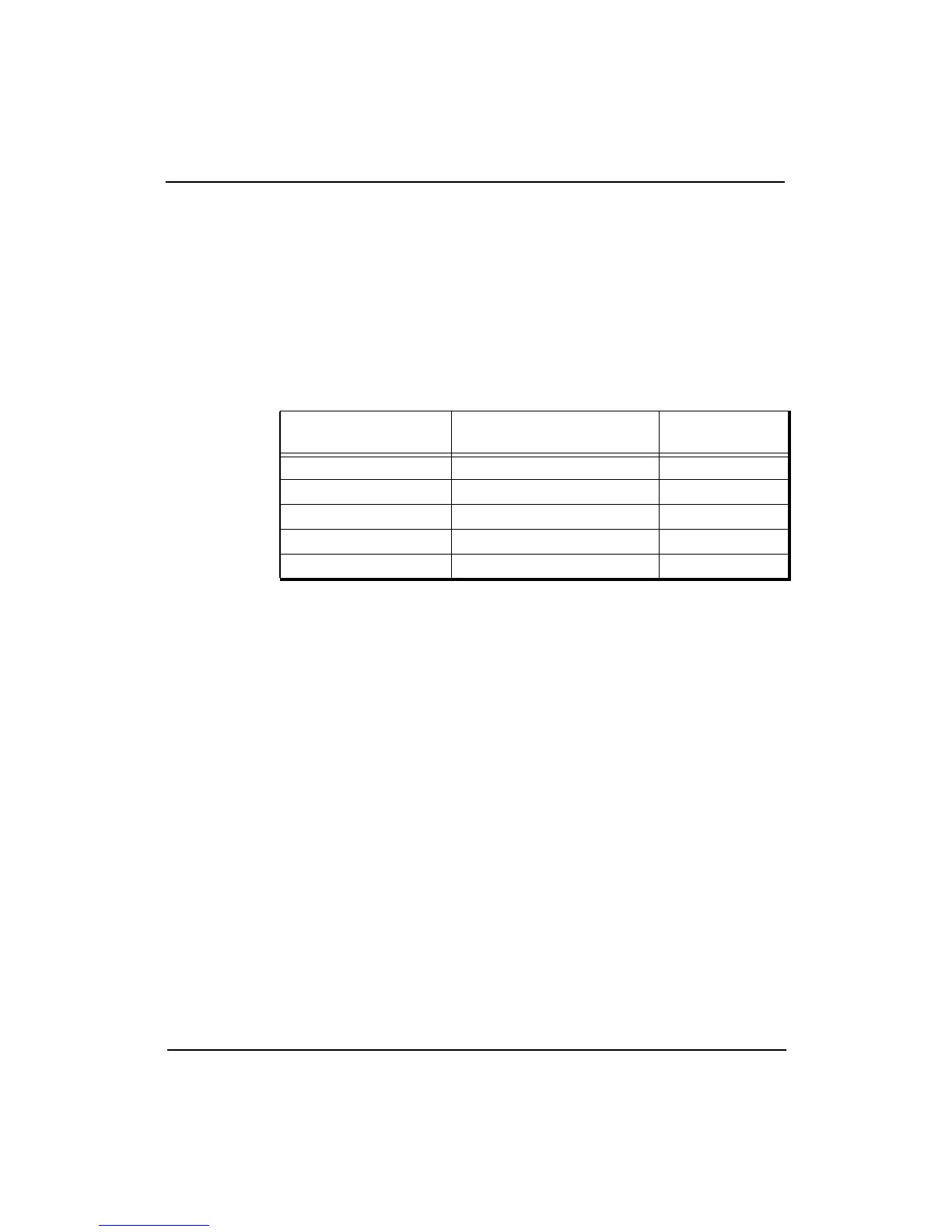

Table 12-7 shows the maximum transmit data rates for a given set of

secondary cache parameters, based on a PClock-to-SClock divisor of 2. To

find the maximum allowable secondary cache write cycle time and

secondary cache access time, multiply the maximum secondary cache

numbers for each pattern by:

(PClock_to_SClock_Divisor)/2

The minimum number for these parameters is always the minimum access

time supported by processor.

Table 12-7 Maximum Transmit Data Rates

Independent Transmissions on the SysAD Bus

In most applications, the SysAD bus is a point-to-point connection,

running from the processor to a bidirectional registered transceiver

residing in an external agent. For these applications, the SysAD bus has

only two possible drivers, the processor or the external agent.

Certain applications may require connection of additional drivers and

receivers to the SysAD bus, to allow transmissions over the SysAD bus

that the processor is not involved in. These are called independent

transmissions. To effect an independent transmission, the external agent

must coordinate control of the SysAD bus by using arbitration handshake

signals and external null requests.

Secondary Cache

Write Cycle Time

Maximum Data Rate

Best Data

Pattern

1-4 PCycles 1 Double/1 SClock Cycle D

5-6 PCycles 2 Doubles/3 SClock Cycles DDx

7-8 PCycles 1 Double/2 SClock Cycles DDxx

9-10 PCycles 2 Doubles/5 SClock Cycles DDxxx

11-12 PCycles 1 Double/3 SClock Cycles DDxxxx

Loading...

Loading...