MIPS R4000 Microprocessor User's Manual 115

CPU Exception Processing

Error Checking and Correcting (ECC) Register (26)

The 8-bit Error Checking and Correcting (ECC) register reads or writes either

secondary-cache data ECC bits or primary-cache data parity bits for cache

initialization, cache diagnostics, or cache error processing. (Tag ECC and

parity are loaded from and stored to the TagLo register.)

The ECC register is loaded by the Index Load Tag CACHE operation.

Content of the ECC register is:

• written into the primary data cache on store instructions

(instead of the computed parity) when the CE bit of the Status

register is set

• substituted for the computed instruction parity for the CACHE

operation Fill

• XORed into the secondary cache computed ECC for the

following primary data cache CACHE operations: Index Write

Back Invalidate, Hit Write Back, and Hit Write Back Invalidate.

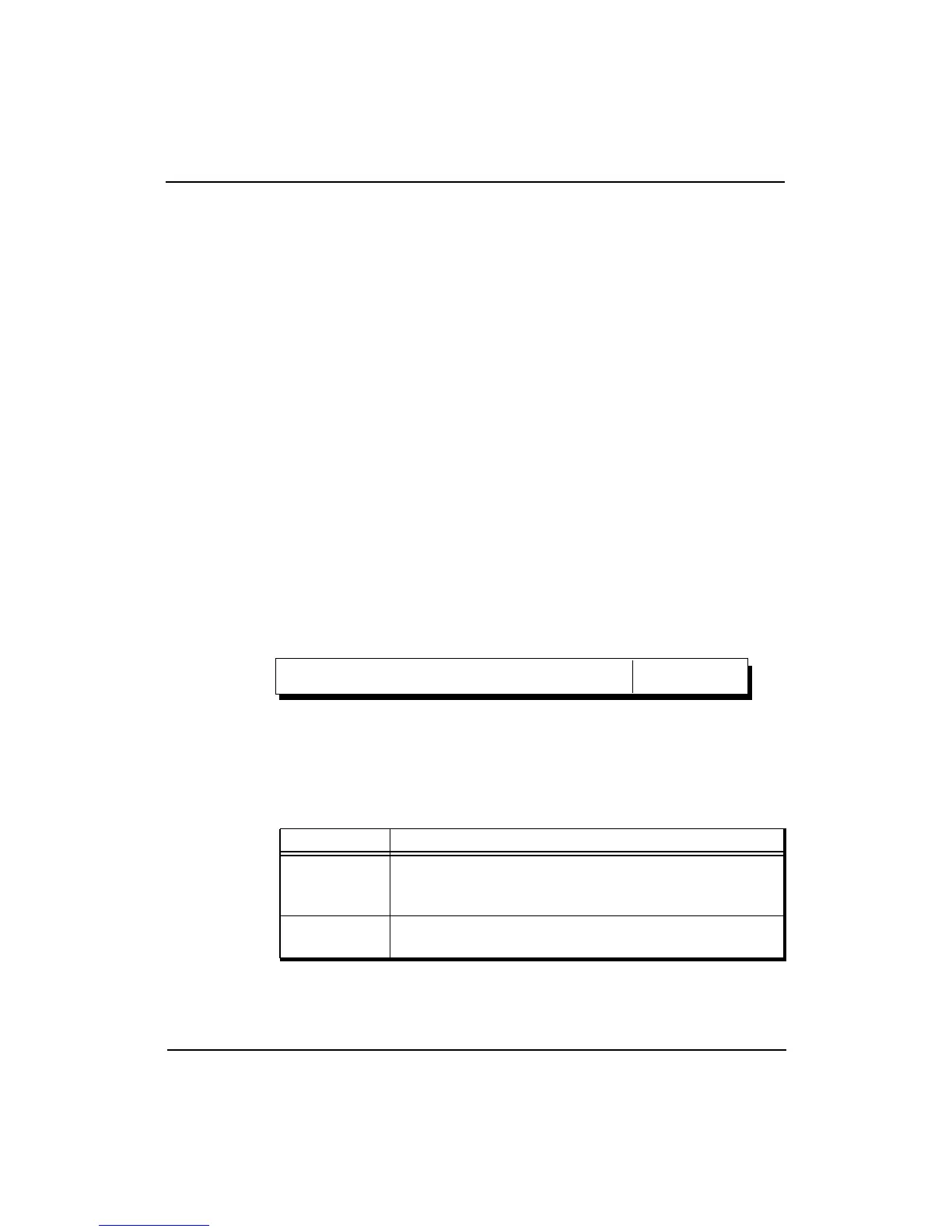

Figure 5-11 shows the format of the ECC register; Table 5-9 describes the

register fields.

Figure 5-11 ECC Register Format

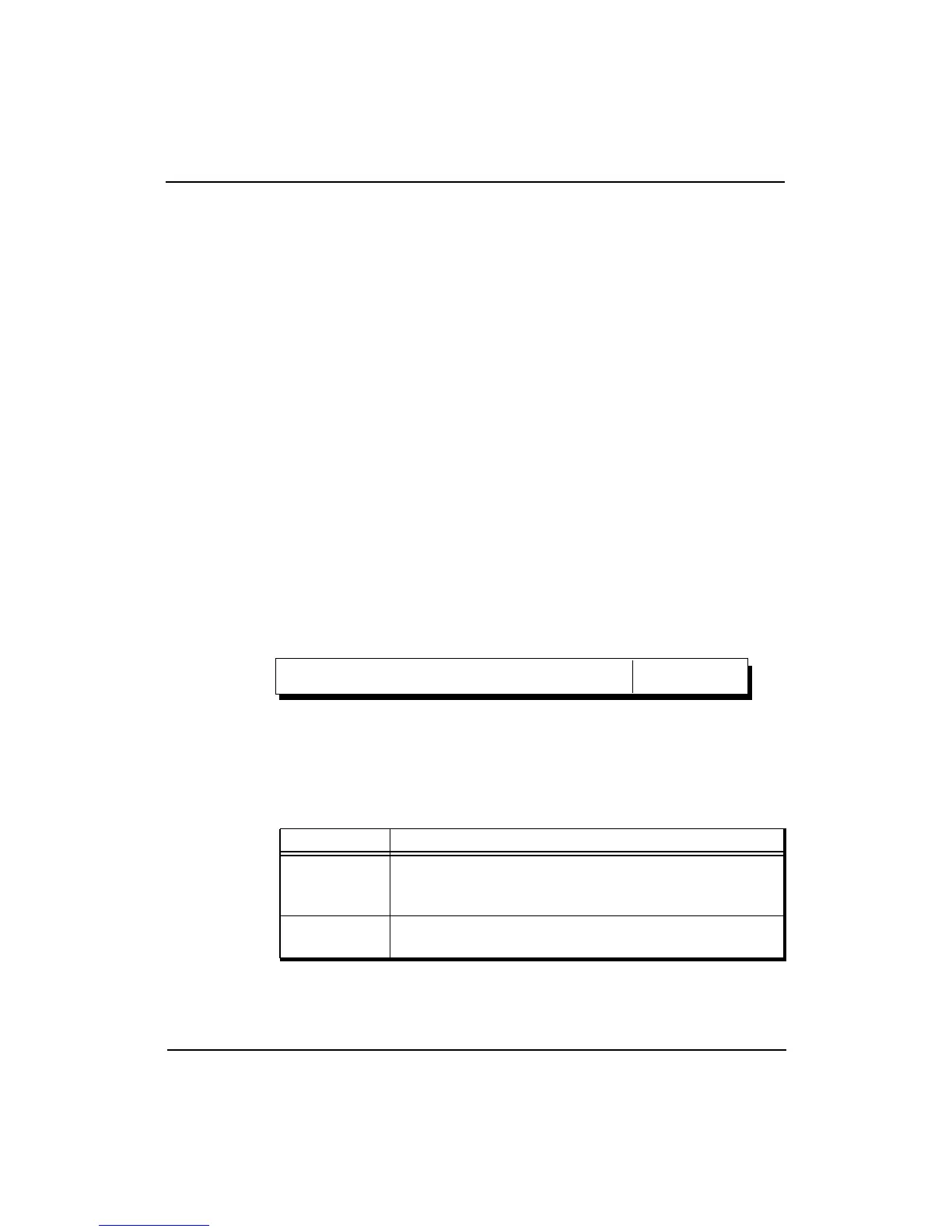

Table 5-9 ECC Register Fields

Field Description

ECC

An 8-bit field specifying the ECC bits read from or

written to a secondary cache, or the even byte parity bits

to be read from or written to a primary cache.

0

Reserved. Must be written as zeroes, and returns zeroes

when read.

ECC Register

31

24 8

807

0 ECC

Loading...

Loading...