Chapter 15

402 MIPS R4000 Microprocessor User's Manual

15.1 Hardware Interrupts

The six CPU hardware interrupts can be caused by external write requests

to the R4000SC, R4000MC, and R4000PC, or can be caused through

dedicated interrupt pins. These pins are latched into an internal register

by the rising edge of SClock. The R4000MC and R4000SC packages

support a single interrupt pin, Int*(0). The R4000PC package supports six

interrupt pins, Int*(5:0).

15.2 Nonmaskable Interrupt (NMI)

The nonmaskable interrupt is caused either by an external write request to

the R4000 or by a dedicated pin in the R4000. This pin is latched into an

internal register by the rising edge of SClock.

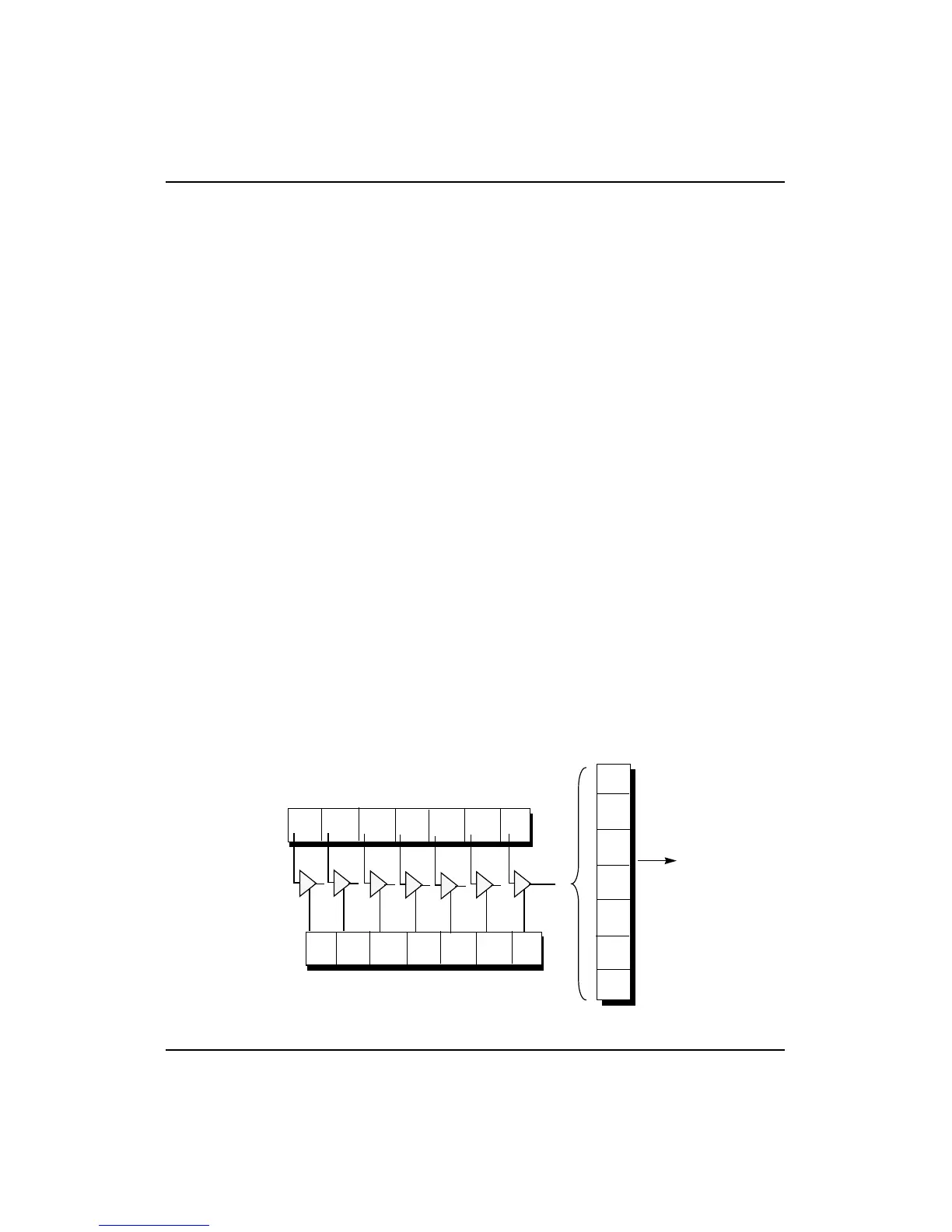

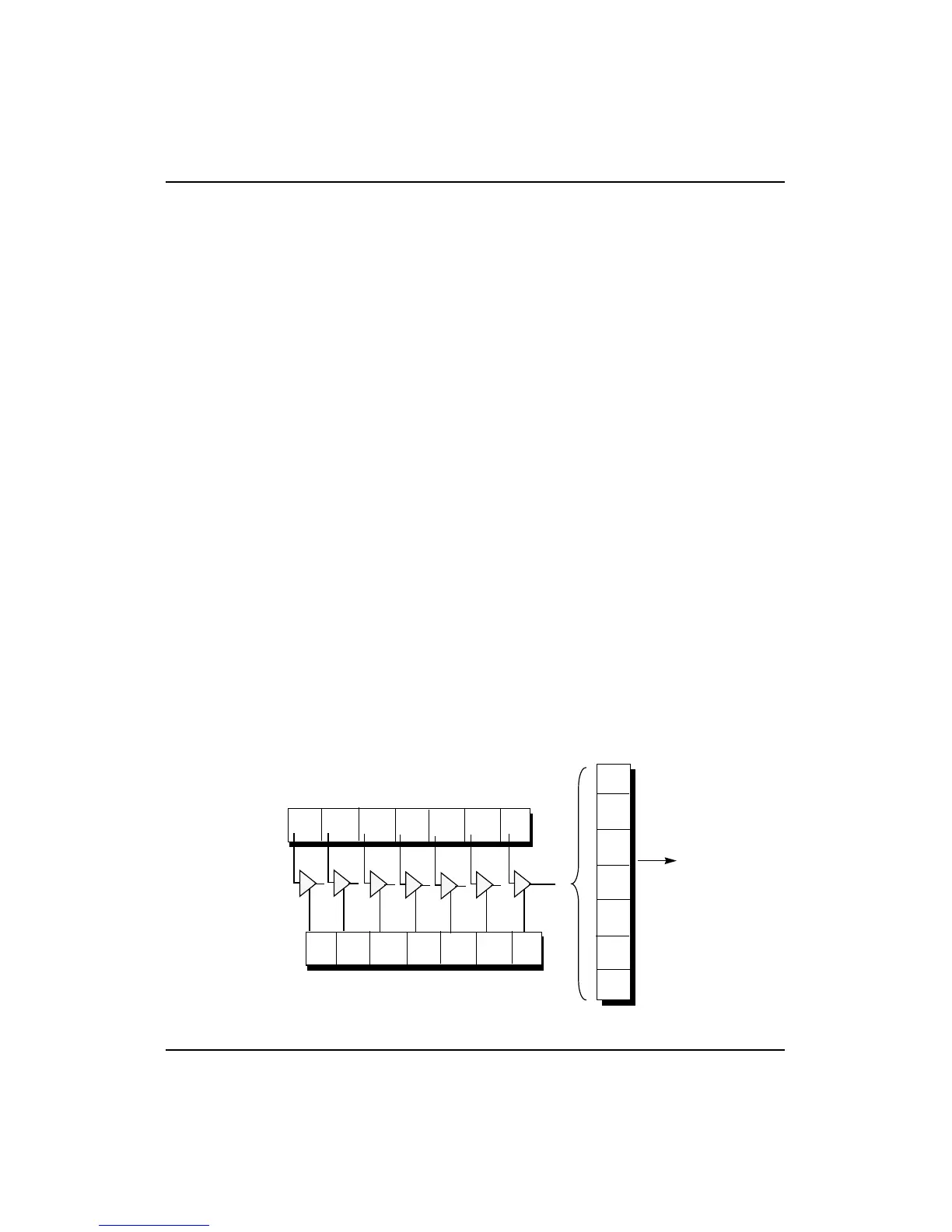

15.3 Asserting Interrupts

External writes to the CPU are directed to various internal resources,

based on an internal address map of the processor. When SysAD[6:4] = 0,

an external write to any address writes to an architecturally transparent

register called the Interrupt register; this register is available for external

write cycles, but not for external reads.

During a data cycle, SysAD[22:16] are the write enables for the seven

individual Interrupt register bits and SysAD[6:0] are the values to be

written into these bits. This allows any subset of the Interrupt register to

be set or cleared with a single write request. Figure 15-1 shows the

mechanics of an external write to the Interrupt register.

Figure 15-1 Interrupt Register Bits and Enables

32

01

5

46

19 18

1617

21

2022

SysAD(6:0)

Interrupt Value

SysAD(22:16)

Write Enables

Interrupt register

See Figures 15-1,

15-2, and 15-3.

2

1

0

4

3

5

6

Loading...

Loading...