MIPS R4000 Microprocessor User's Manual 209

R4000 Processor Signal Descriptions

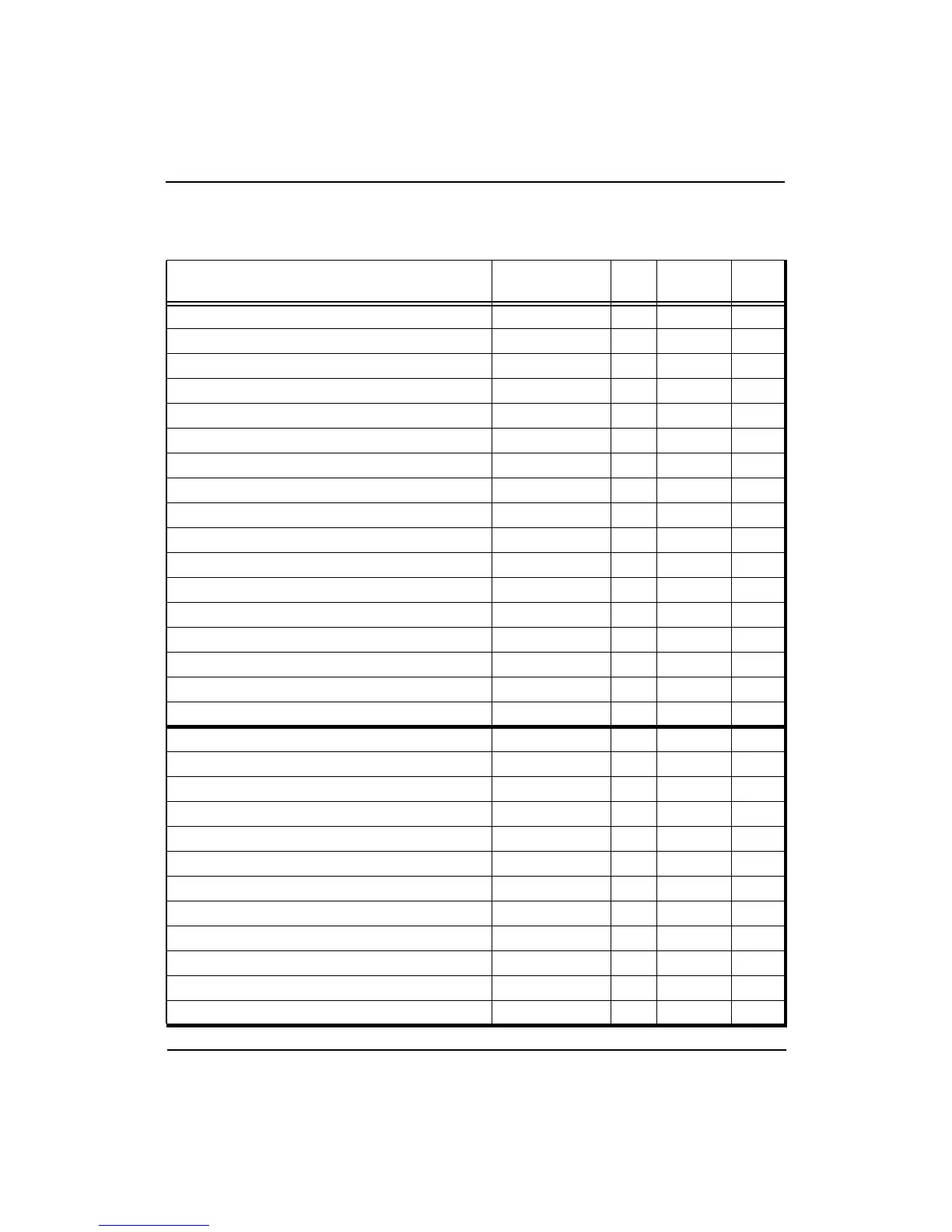

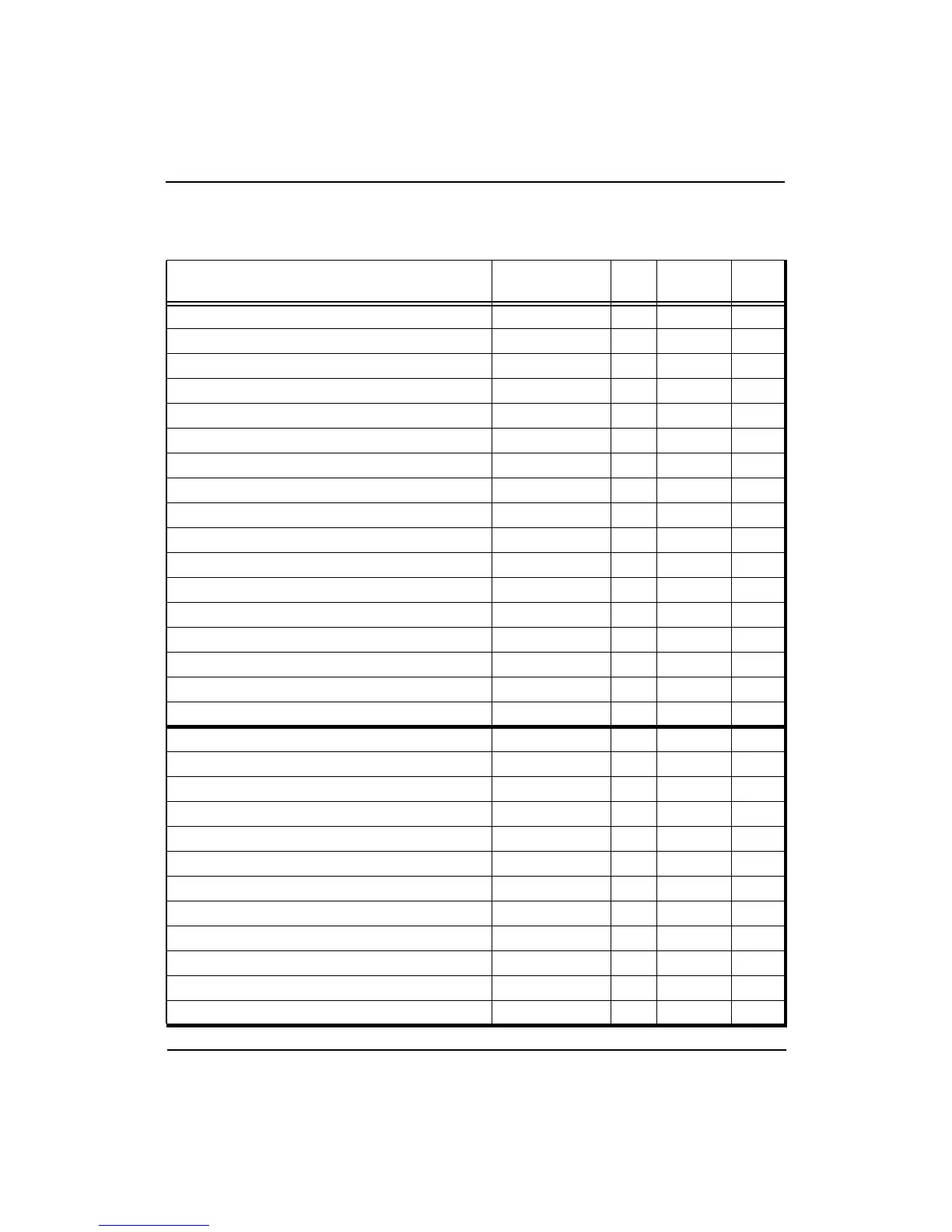

8.7 Signal Summary

Table 8-7 R4000SC/MC Processor Signal Summary

Description Name I/O

Asserted

State

3-State

Secondary cache data bus SCData(127:0) I/O High Yes

Secondary cache data ECC bus SCDChk(15:0) I/O High Yes

Secondary cache tag bus SCTag(24:0) I/O High Yes

Secondary cache tag ECC bus SCTChk(6:0) I/O High Yes

Secondary cache address bus SCAddr(17:1) O High No

Secondary cache address LSB SCAddr0Z O High No

Secondary cache address LSB SCAddr0Y O High No

Secondary cache address LSB SCAddr0X O High No

Secondary cache address LSB SCAddr0W O High No

Secondary cache address parity bus SCAPar(2:0) O High No

Secondary cache output enable SCOE* O Low No

Secondary cache write enable SCWrZ* O Low No

Secondary cache write enable SCWrY* O Low No

Secondary cache write enable SCWrX* O Low No

Secondary cache write enable SCWrW* O Low No

Secondary cache data chip select SCDCS* O Low No

Secondary cache tag chip select SCTCS* O Low No

System address/data bus SysAD(63:0) I/O High Yes

System address/data check bus SysADC(7:0) I/O High Yes

System command/data identifier bus SysCmd(8:0) I/O High Yes

System command/data identifier bus parity SysCmdP I/O High Yes

Valid input ValidIn* I Low No

Valid output ValidOut* O Low No

External request ExtRqst* I Low No

Release interface Release* O Low No

Read ready RdRdy* I Low No

Write ready WrRdy* I Low No

Invalidate acknowledge IvdAck* I Low No

Invalidate error IvdErr* I Low No

Loading...

Loading...