Chapter 5

122 MIPS R4000 Microprocessor User's Manual

Exception Vector Locations

The Reset, Soft Reset, and NMI exceptions are always vectored to the

dedicated Reset exception vector at an uncached and unmapped address.

Addresses for all other exceptions are a combination of a vector offset and

a base address.

The boot-time vectors (when BEV = 1 in the Status register) are at

uncached and unmapped addresses. During normal operation (when

BEV = 0) the regular exceptions have vectors in cached address spaces;

Cache Error is always at an uncached address so that cache error handling

can bypass a suspect cache.

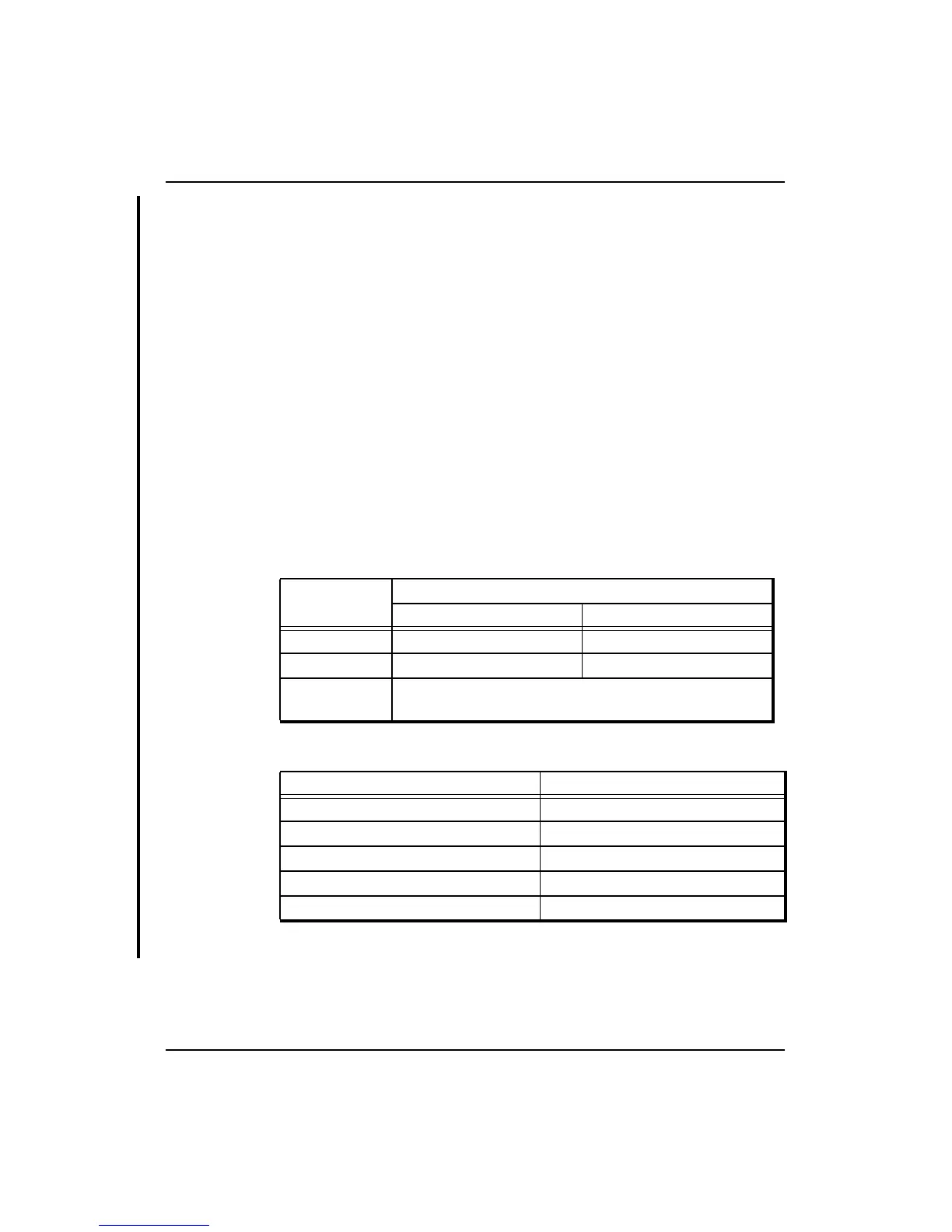

Table 5-11 shows the 64-bit-mode vector base address for all exceptions;

the 32-bit mode address is the low-order 32 bits (for instance, the base

address for NMI in 32-bit mode is 0xBFC0 0000).

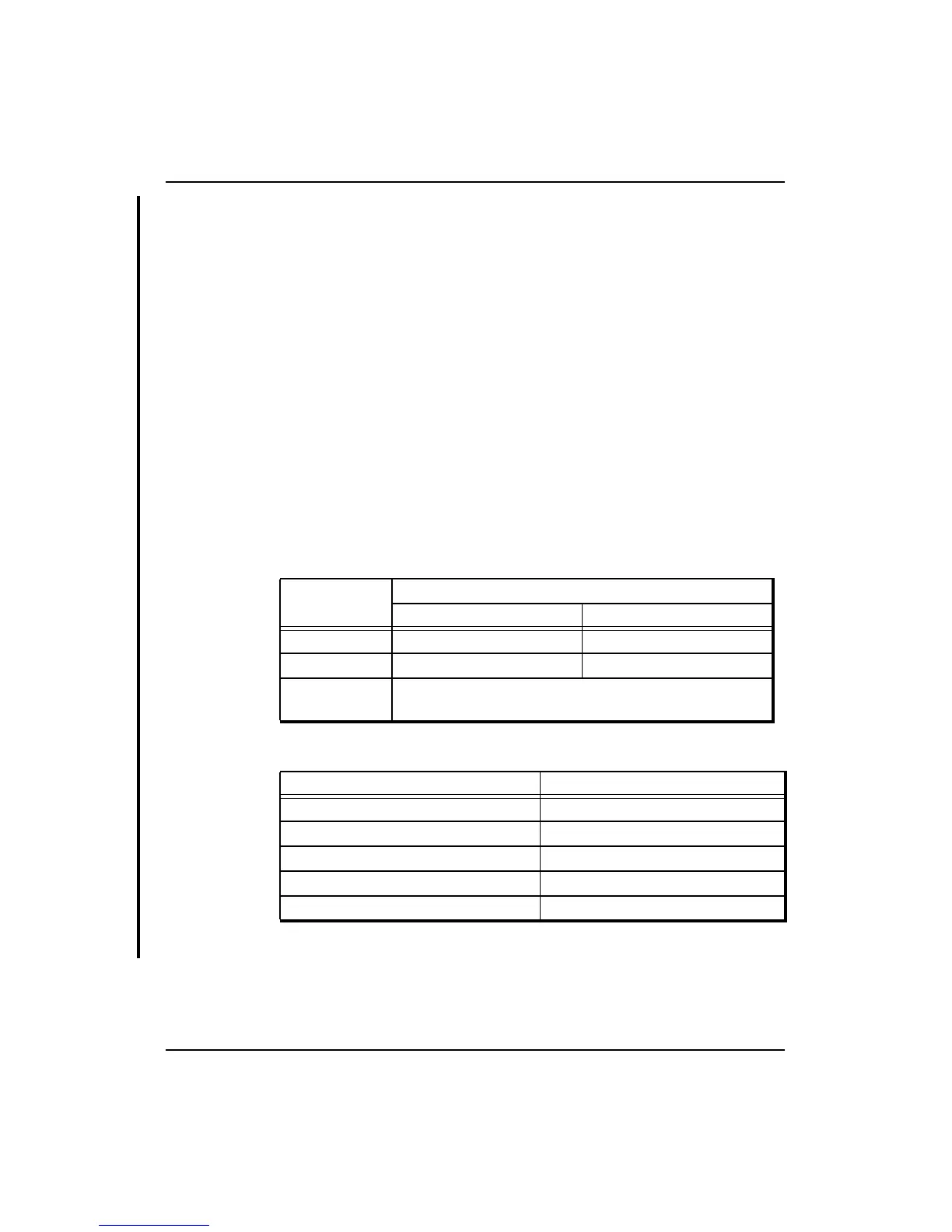

Table 5-12 shows the vector offset added to the base address to create the

exception address.

Table 5-11 Exception Vector Base Addresses

Table 5-12 Exception Vector Offsets

Exception

BEV

01

Cache Error 0xFFFF FFFF A000 0000 0xFFFF FFFF BFC0 0200

Others 0xFFFF FFFF 8000 0000 0xFFFF FFFF BFC0 0200

Reset, NMI,

Soft Reset

0xFFFF FFFF BFC0 0000

Exception R4000 Processor Vector Offset

TLB refill, EXL = 0 0x000

XTLB refill, EXL = 0 (X = 64-bit TLB) 0x080

Cache Error 0x100

Others 0x180

Reset, Soft Reset, NMI none

Loading...

Loading...