Chapter 2

40 MIPS R4000 Microprocessor User's Manual

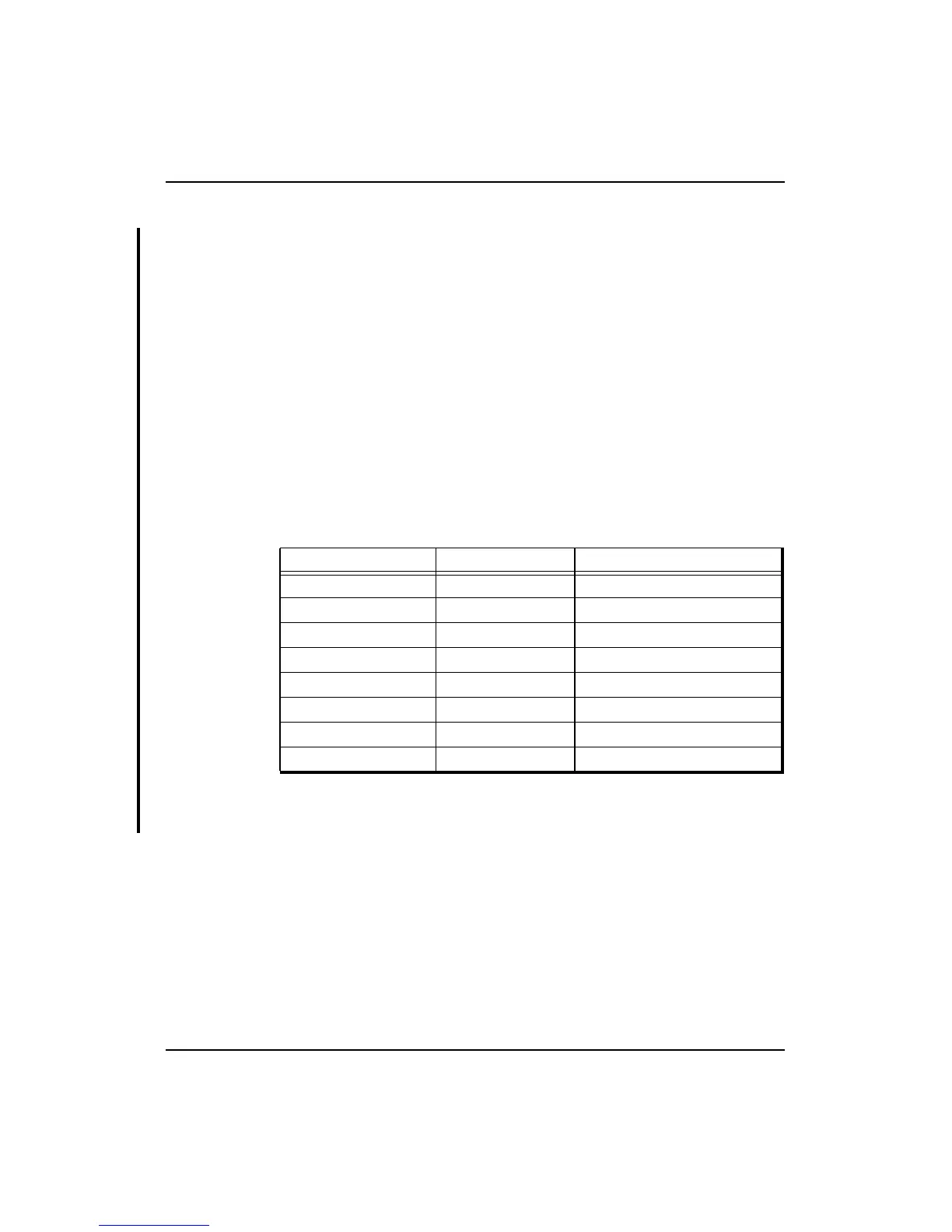

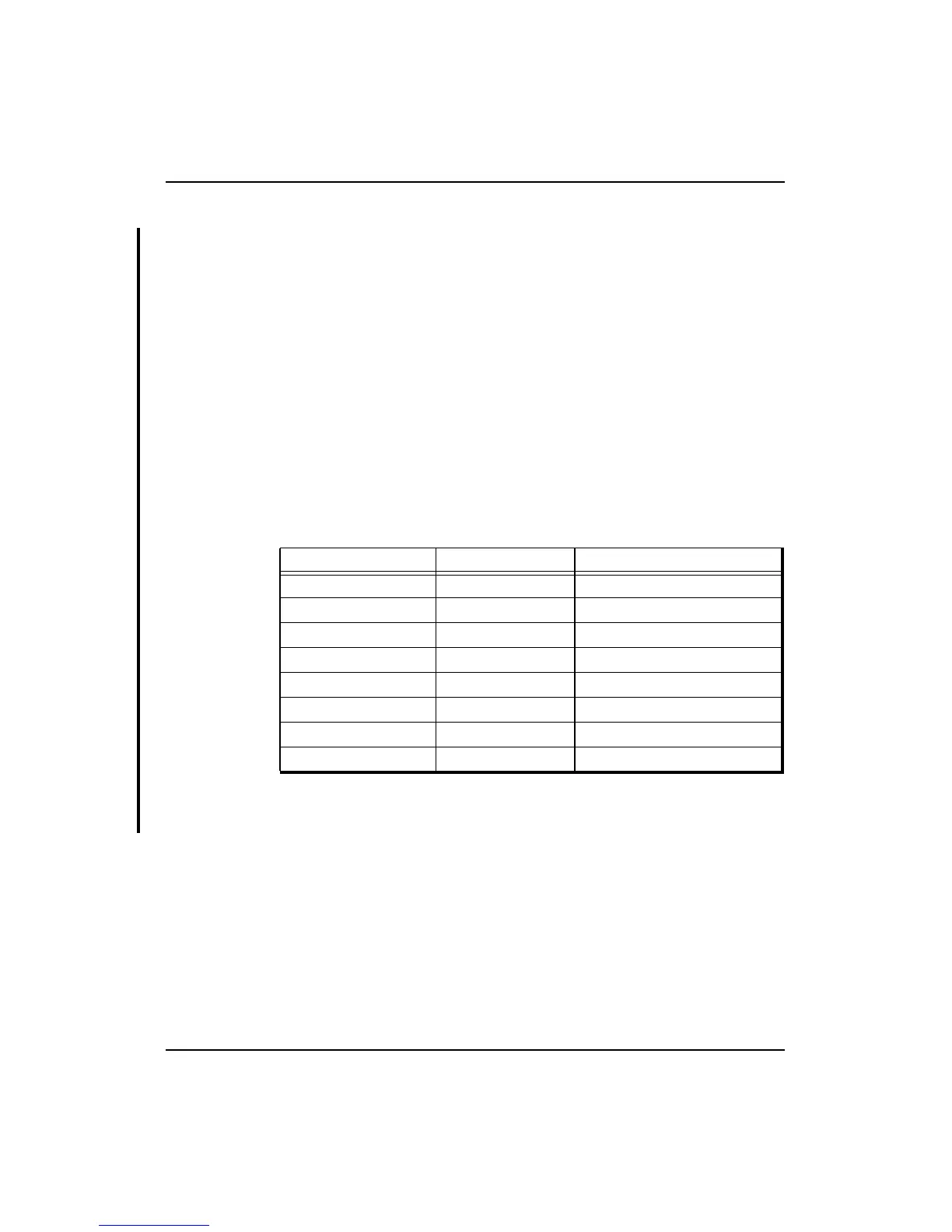

Cycle Timing for Multiply and Divide Instructions

Any multiply instruction in the integer pipeline is transferred to the

multiplier as remaining instructions continue through the pipeline; the

product of the multiply instruction is saved in the HI and LO registers.

If the multiply instruction is followed by an MFHI or MFLO before the

product is available, the pipeline interlocks until this product does become

available.

Table 2-2 gives the execution time for integer multiply and divide

operations. The “Total Cycles” column gives the total number of cycles

required to execute the instruction. The “Overlap” column gives the

number of cycles that overlap other CPU operations; that is, the number of

cycles required between the present instruction and a subsequent MFHI or

MFLO without incurring an interlock. If this value is zero, the operation

is not performed in parallel with any other CPU operation.

Table 2-2 Multiply/Divide Instruction Cycle Timing

For more information about computational instructions, refer to the

individual instruction as described in Appendix A.

Instruction Total Cycles Overlap

MULT 12 10

MULTU 12 10

DIV 75 0

DIVU 75 0

DMULT 20 18

DMULTU 20 18

DDIV 139 0

DDIVU 139 0

Loading...

Loading...