Chapter 1

24 MIPS R4000 Microprocessor User's Manual

Data Formats and Addressing

The R4000 processor uses four data formats: a 64-bit doubleword, a 32-bit

word, a 16-bit halfword, and an 8-bit byte. Byte ordering within each of

the larger data formats—halfword, word, doubleword—can be

configured in either big-endian or little-endian order. Endianness refers

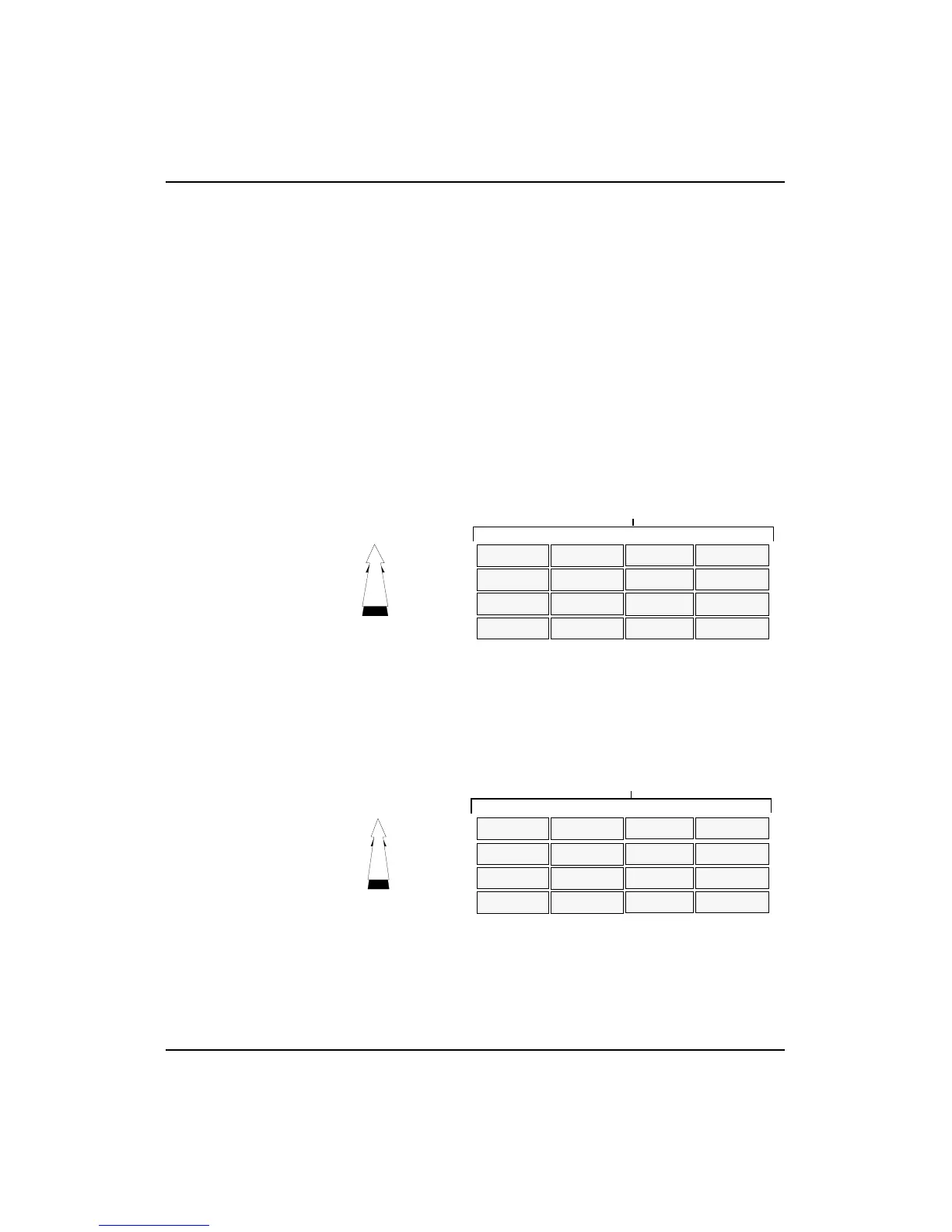

to the location of byte 0 within the multi-byte data structure. Figures 1-4

and 1-5 show the ordering of bytes within words and the ordering of

words within multiple-word structures for the big-endian and little-

endian conventions.

When the R4000 processor is configured as a big-endian system, byte 0 is

the most-significant (leftmost) byte, thereby providing compatibility with

MC 68000

and IBM 370

conventions. Figure 1-4 shows this

configuration.

Figure 1-4 Big-Endian Byte Ordering

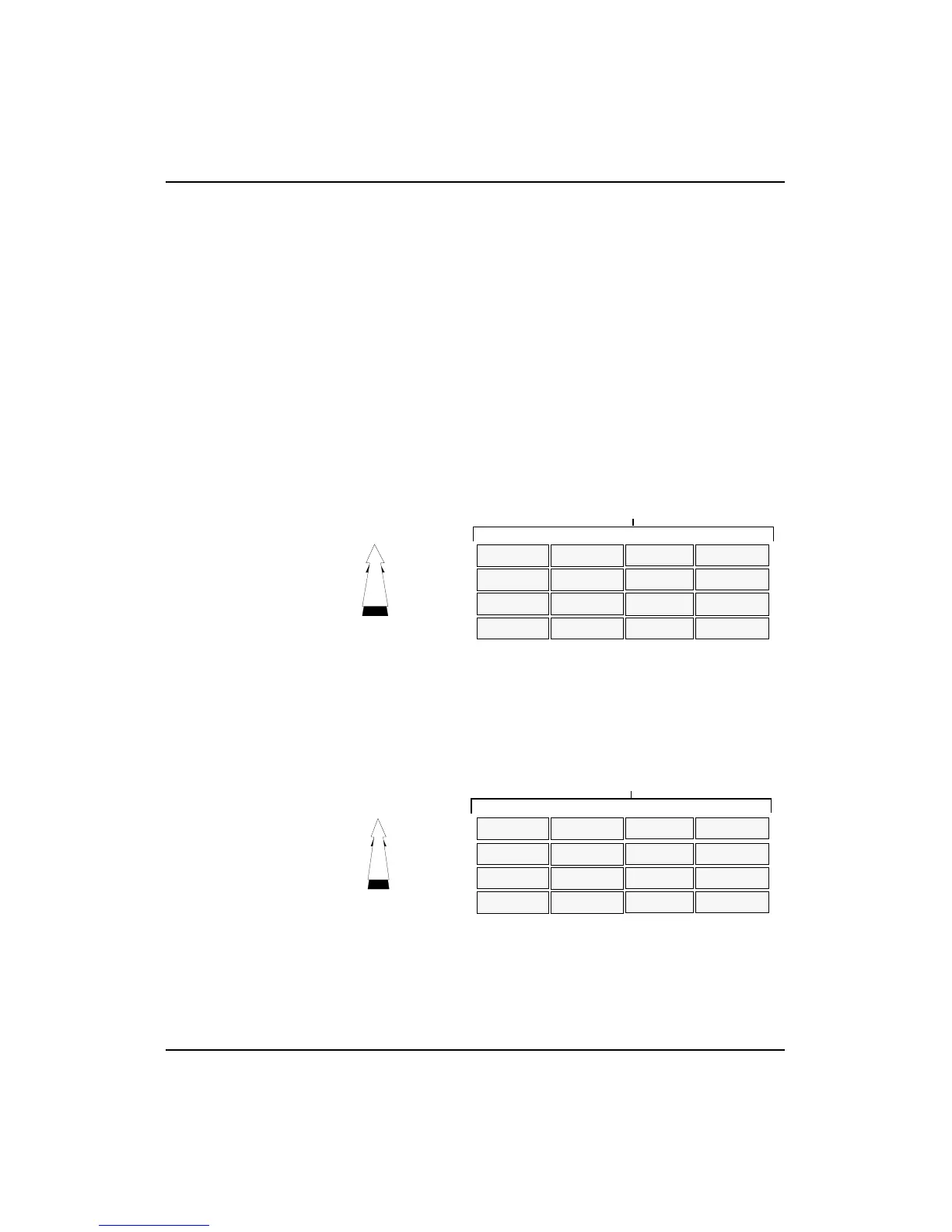

When configured as a little-endian system, byte 0 is always the least-

significant (rightmost) byte, which is compatible with iAPX

x86 and DEC

VAX

conventions. Figure 1-5 shows this configuration.

Figure 1-5 Little-Endian Byte Ordering

Higher

Address

Lower

Address

Word

4

8

12

Address

Bit #

89 1110

45 76

01 32

12 13 1514

0

31 24 23 16 15 8 7 0

Higher

Address

Lower

Address

Word

4

8

12

Address

31 24 23 16 15 8 7 0

Bit #

11 10 89

76 45

32 01

15 14 1213

0

Loading...

Loading...