Chapter 6

164 MIPS R4000 Microprocessor User's Manual

6.4 Floating-Point Formats

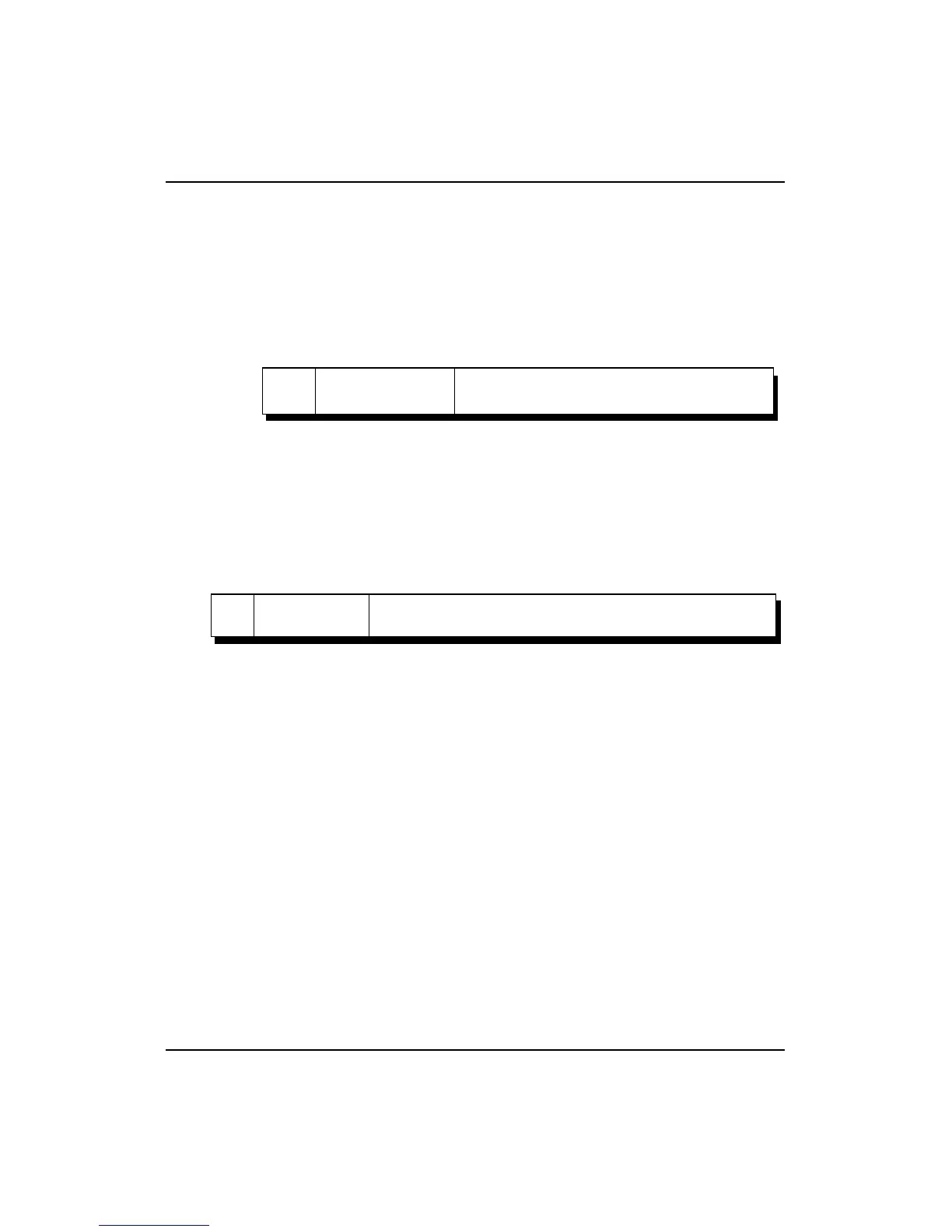

The FPU performs both 32-bit (single-precision) and 64-bit (double-

precision) IEEE standard floating-point operations. The 32-bit single-

precision format has a 24-bit signed-magnitude fraction field (f+s) and an

8-bit exponent (e), as shown in Figure 6-6.

Figure 6-6 Single-Precision Floating-Point Format

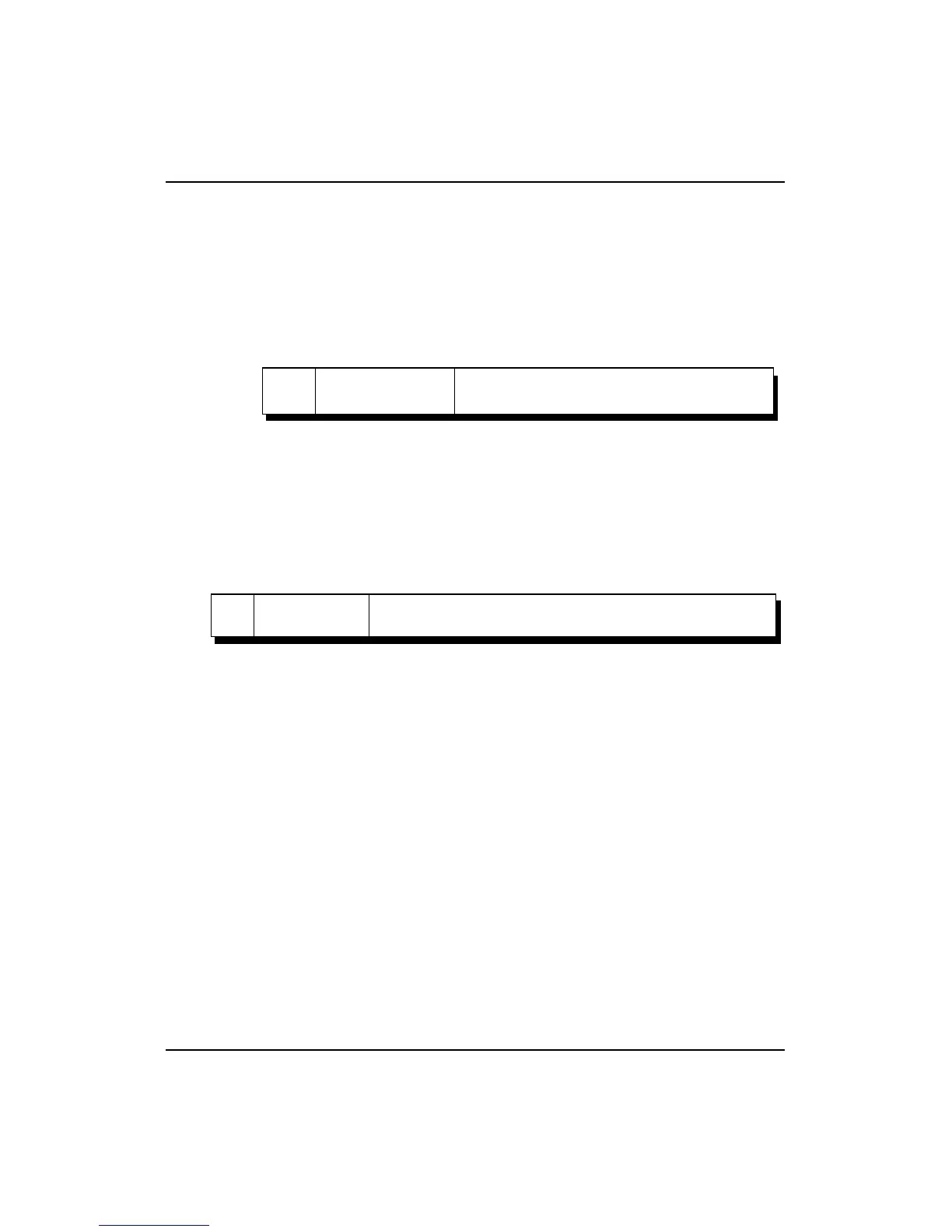

The 64-bit double-precision format has a 53-bit signed-magnitude fraction

field (f+s) and an 11-bit exponent, as shown in Figure 6-7.

Figure 6-7 Double-Precision Floating-Point Format

As shown in the above figures, numbers in floating-point format are

composed of three fields:

• sign field, s

• biased exponent, e = E + bias

• fraction, f = .b

1

b

2

....b

p–1

The range of the unbiased exponent E includes every integer between the

two values E

min

and E

max

inclusive, together with two other reserved

values:

•E

min

-1 (to encode 0 and denormalized numbers)

•E

max

+1 (to encode

∞

and NaNs [Not a Number])

For single- and double-precision formats, each representable nonzero

numerical value has just one encoding.

31 30 23 22 0

FractionSign Exponent

2318

se f

63 62 52 51 0

FractionSign Exponent

52111

se f

Loading...

Loading...