MIPS R4000 Microprocessor User's Manual 181

Floating-Point Unit

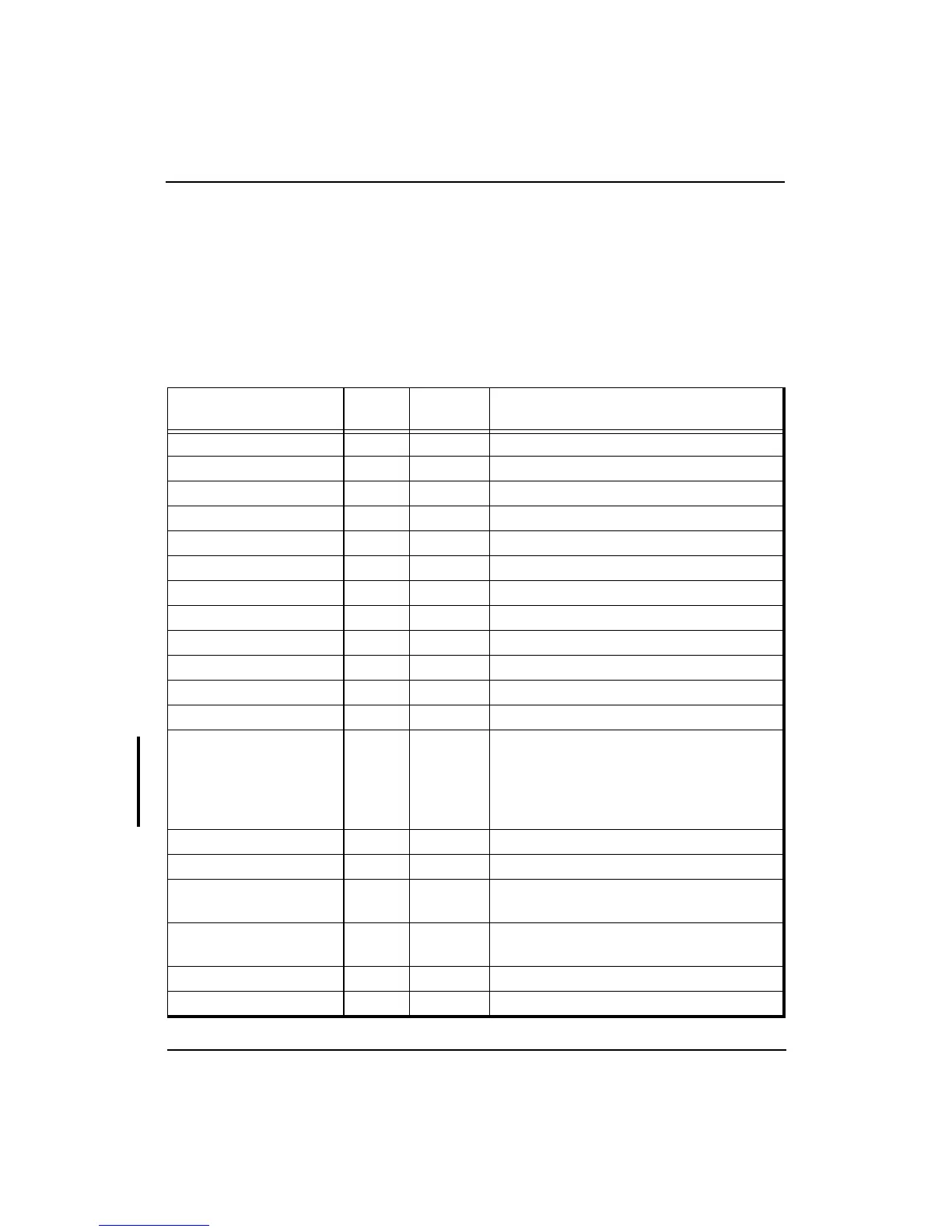

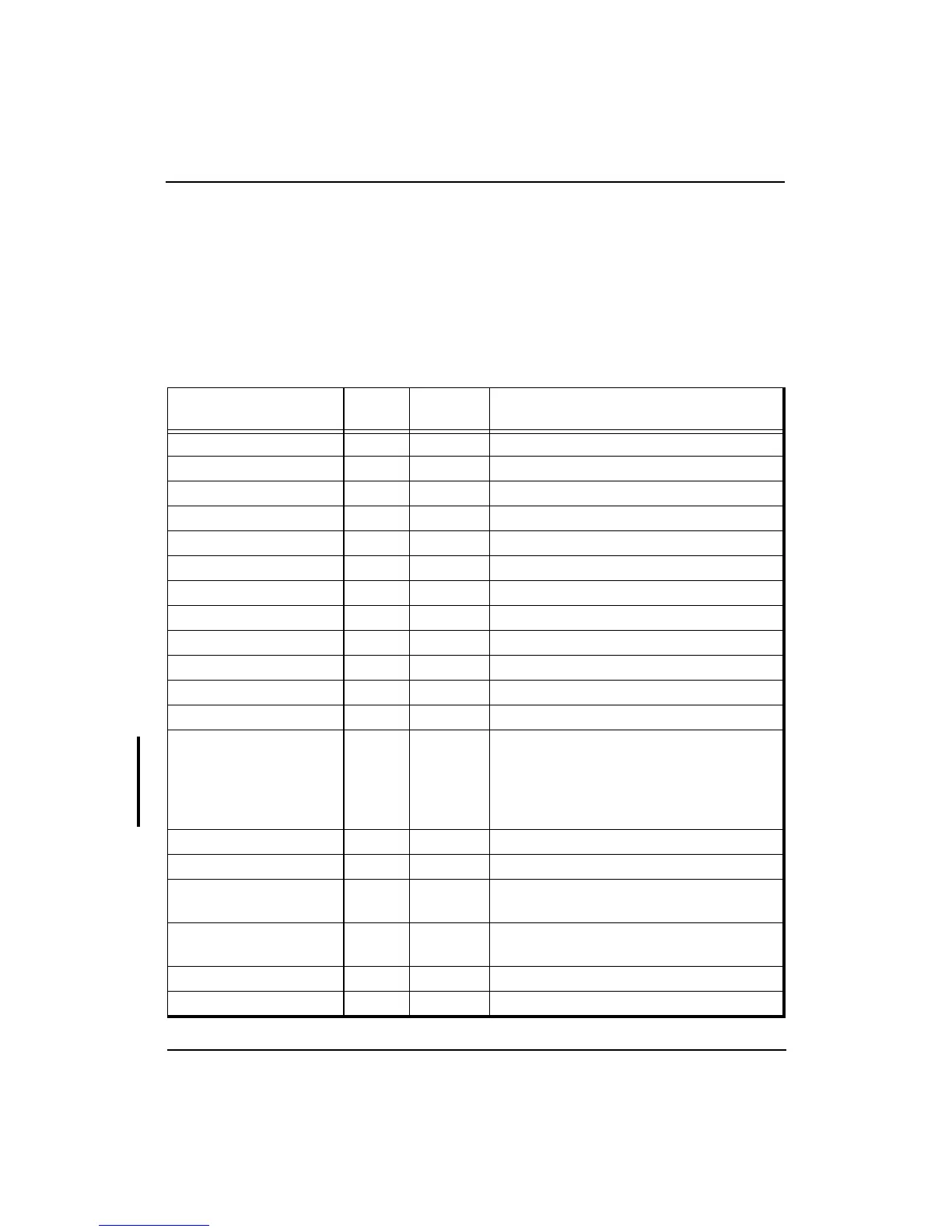

Instruction Latency, Repeat Rate, and Pipeline Stage Sequences

Table 6-16 lists the latency and repeat rate between instructions, together

with the sequence of pipeline stages for each instruction. For example, the

latency of the ADD.[S,D] is 4, which means it takes four processor cycles

to complete. The Repeat Rate column indicates how soon an instruction

can be repeated; for example, an ADD.[S,D] can be repeated after the

conclusion of the third pipeline stage.

Table 6-16 Latency, Repeat Rate, and Pipe Stages of FPU Instructions

Instruction Type Latency

Repeat

Rate

Pipeline Stage

Sequence

MOV.[S,D] 1 1 EX

ADD.[S,D] 4 3 U→ S+A→ A+R→ R+S

SUB.[S,D] 4 3 U→ S+A→ A+R→ R+S

C.COND.[S,D] 3 2 U→ A→ R

NEG.[S,D] 2 1 U→ S

ABS.[S,D] 2 1 U→ S

CVT.S.W 6 5 U→ A→ R→ S→ A→ R

CVT.D.W 5 4 U→ S→ A→ R→ S

CVT.S.L 7 6 U→ A→ R→ S→ S→ A→ R

CVT.D.L 4 3 U→ A→ R→ S

CVT.D.S 2 1 U→ S

CVT.S.D 4 3 U→ S→ A→ R

CVT.[W,L].[S,D] or

ROUND.[W,L].[S,D] or

TRUNC.[W,L].[S,D] or

CEIL.[W,L].[S,D] or

FLOOR.[W,L].[S,D]

43U→ S→ A→ R

MUL.S 7 3 U→ E/M→ M→ M→ N→ N/A→ R

MUL.D 8 4 U→ E/M→ M→ M→ M→ N→ N/A→ R

DIV.S 23 22

U→ S+A→ S+R→ S→ D...D→ D/A→

D/R→ D/A→ D/R→A→R

DIV.D 36 35

U→ A→ R→ D...D→ D/A→ D/R→ D/A →

D/R→ A→ R

SQRT.S 2–54 2–53 U→ E→ A+R→...→ A+R→ A→ R

SQRT.D 2–112 2–111 U→ E→ A+R→...→ A+R→ A→ R

Loading...

Loading...