Chapter 3

58 MIPS R4000 Microprocessor User's Manual

Special Cases

In some instances, the pipeline control state machine is bypassed. This

occurs due to performance considerations or to correctness

considerations, which are described in the following sections.

Performance Considerations

A performance consideration occurs when there is a cache load miss. By

bypassing the pipeline state machine, it is possible to eliminate up to two

cycles of load miss latency. Two techniques, address acceleration and

address prediction, increase performance.

Address Acceleration

Address acceleration bypasses a potential cache miss address. It is relatively

straightforward to perform this bypass since sending the cache miss

address to the secondary cache has no negative impact even if a

subsequent exception nullifies the effect of this cache access. Power is

wasted when the miss is inhibited by some fault, but this is a minor effect.

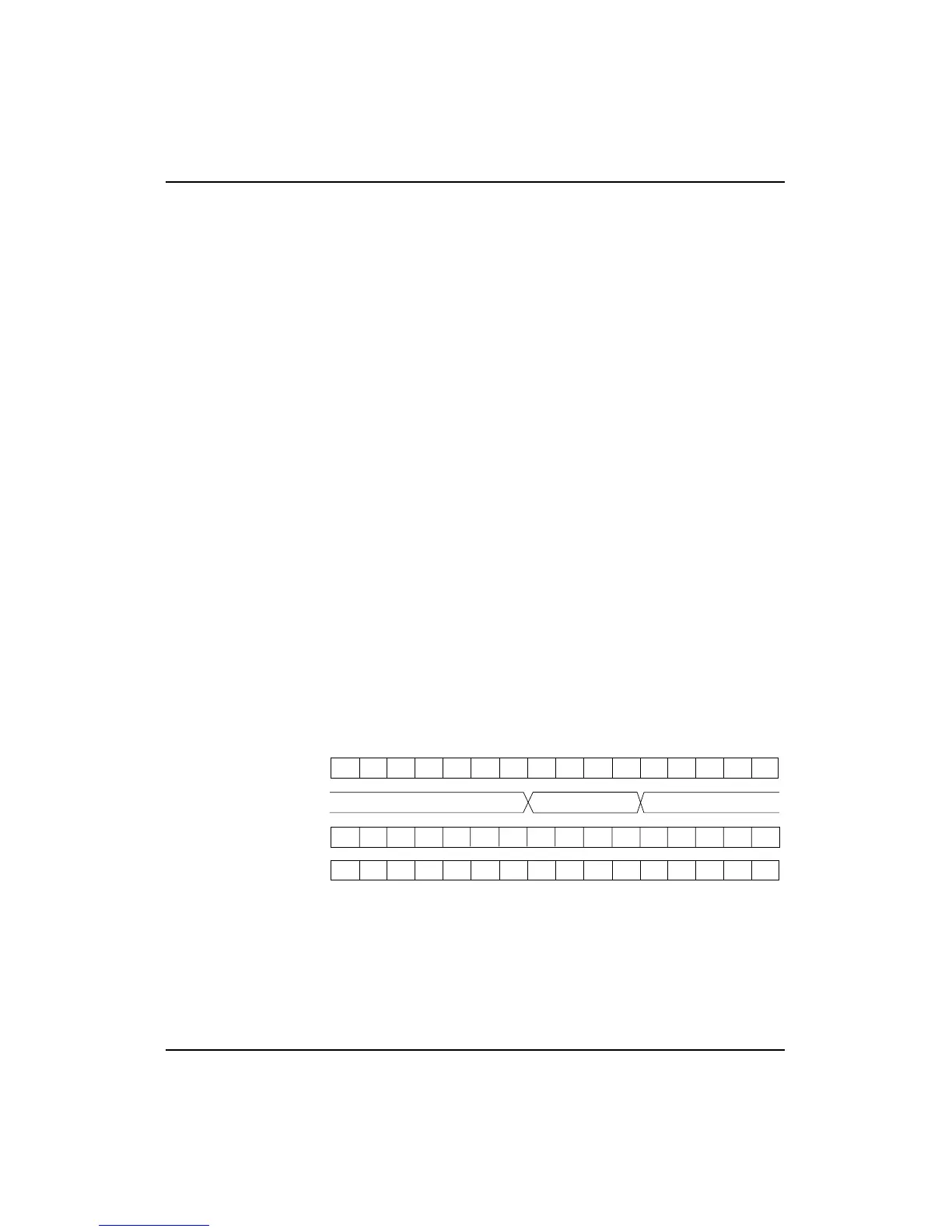

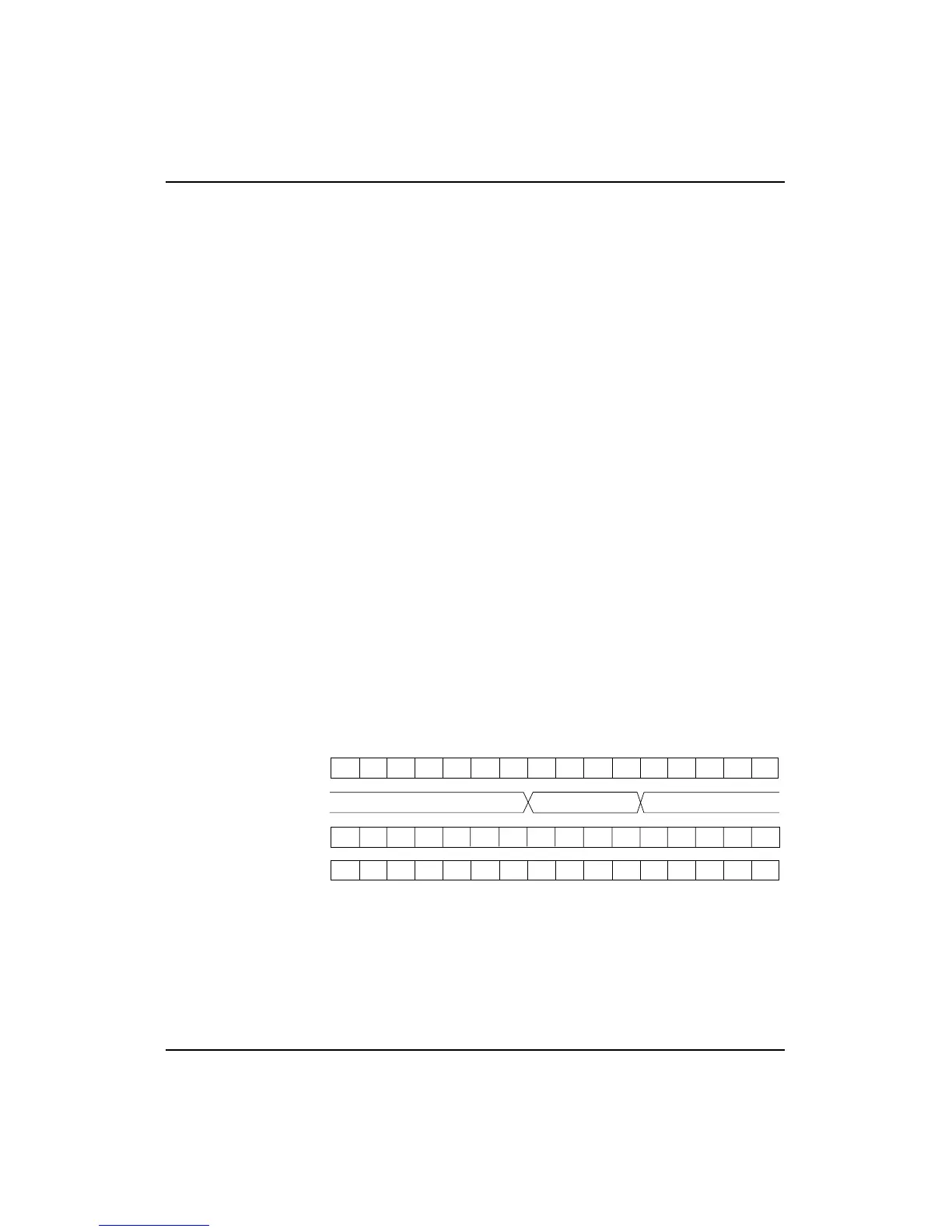

Address Prediction

Another technique used to reduce miss latency is the automatic increment

and transmission of instruction miss addresses following an instruction

cache miss. This form of latency reduction is called address prediction: the

subsequent instruction miss address is predicted to be a simple increment

of the previous miss address. Figure 3-11 shows a cache miss in which the

cache miss address is changed based on the detection of the miss.

Figure 3-11 Load Address Bypassing

Correctness Considerations

An example in which bypassing is necessary to guarantee correctness is a

cache write.

Run Run Run Run Run Run Run Stl Stl Stl Stl Stl Stl Stl Stl Run

Cycle

Restart

Address

Load

IF IS RF EX DF DS TC DF DS TC WB

Rst3

Rst2

Rst1

Cache Index

Loading...

Loading...