Chapter 6

160 MIPS R4000 Microprocessor User's Manual

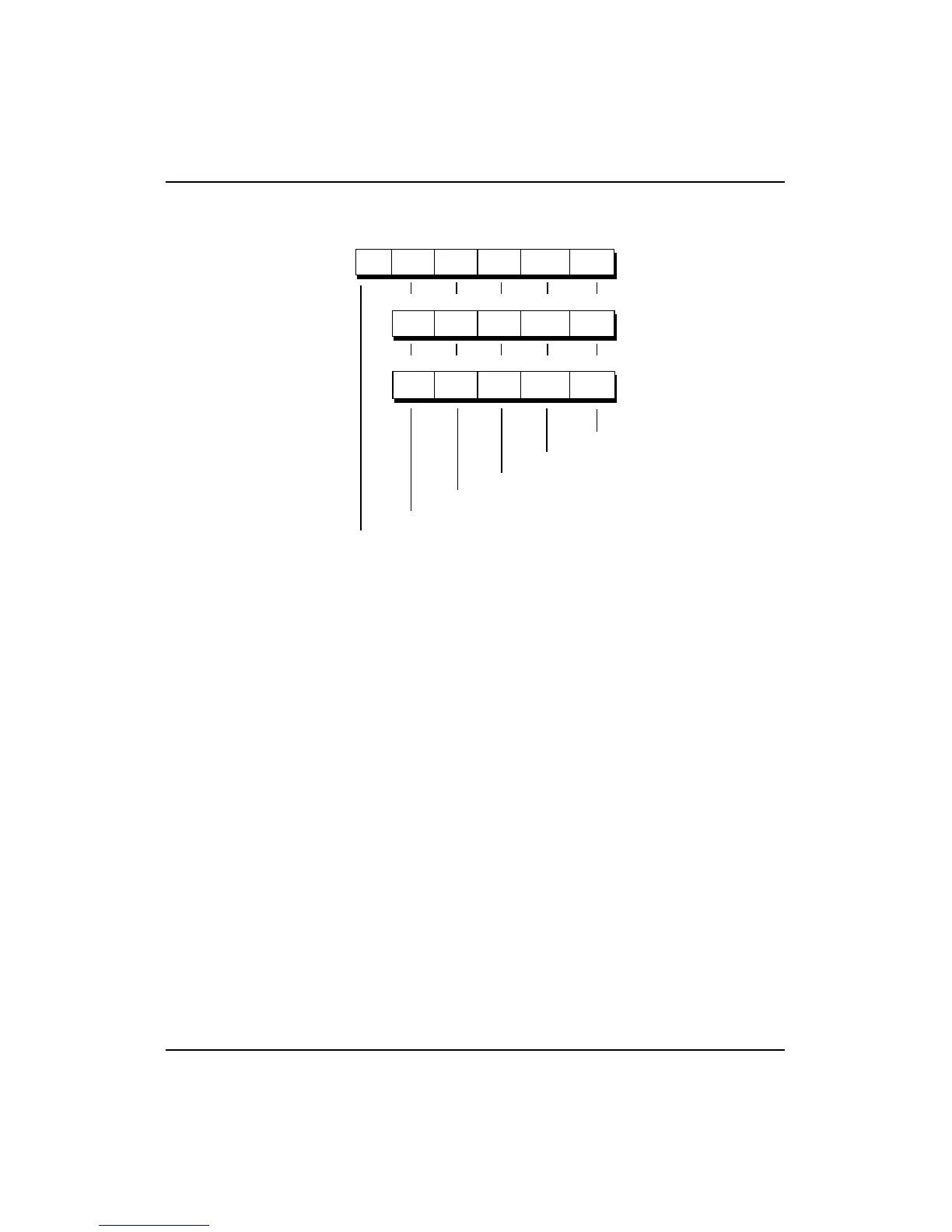

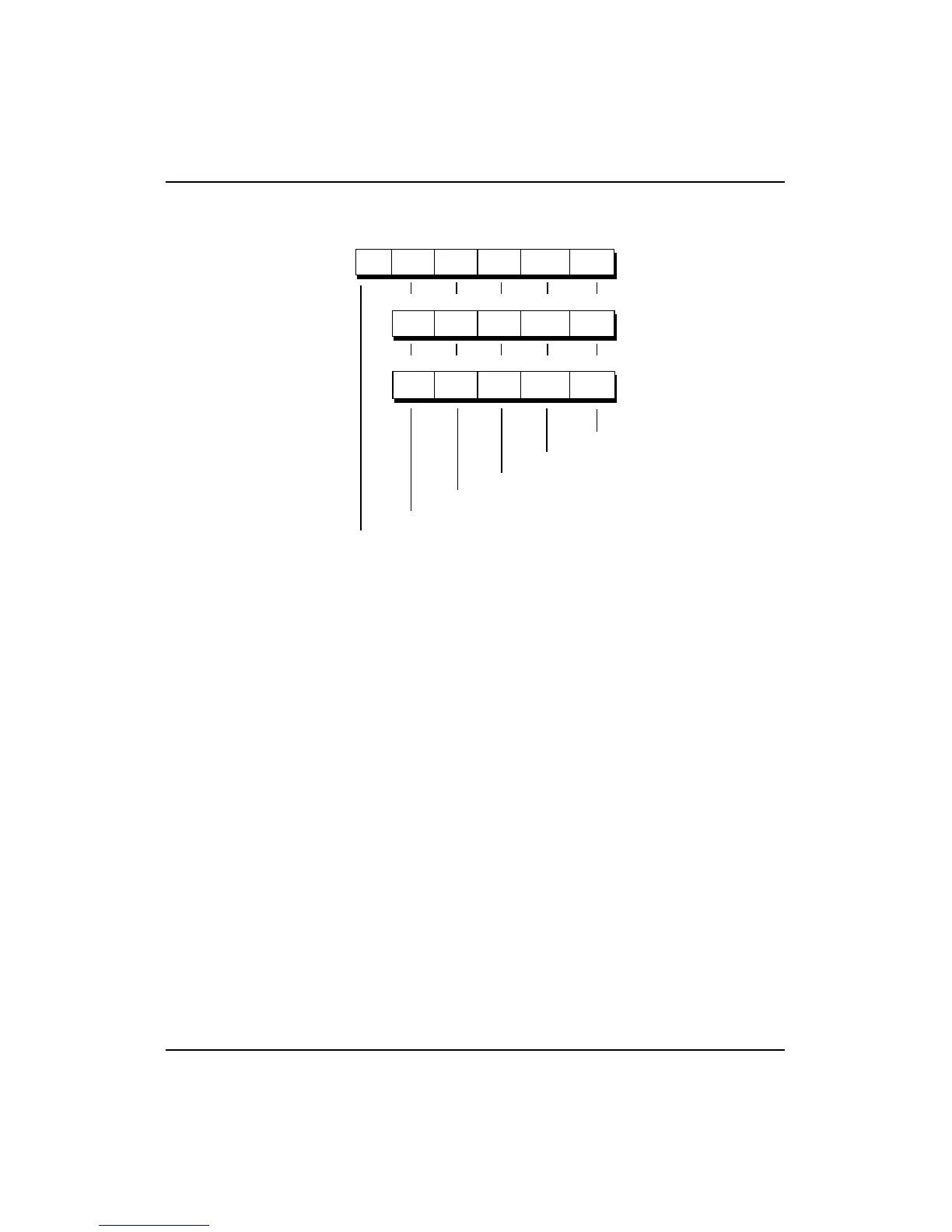

Figure 6-5 Control/Status Register Cause, Flag, and Enable Fields

Accessing the Control/Status Register

When the Control/Status register is read by a Move Control From

Coprocessor 1 (CFC1) instruction, all unfinished instructions in the

pipeline are completed before the contents of the register are moved to the

main processor. If a floating-point exception occurs as the pipeline

empties, the FP exception is taken and the CFC1 instruction is re-executed

after the exception is serviced.

The bits in the Control/Status register can be set or cleared by writing to the

register using a Move Control To Coprocessor 1 (CTC1) instruction.

FCR31 must only be written to when the FPU is not actively executing

floating-point operations; this can be ensured by reading the contents of

the register to empty the pipeline.

EZOUIV

17 16 15 14 13 12

Unimplemented Operation

Invalid Operation

Division by Zero

Inexact Operation

Overflow

Underflow

Bit #

ZO U IV

11 10 9 8 7

Bit #

ZO U IV

6543 2

Bit #

Cause

Bits

Flag

Bits

Enable

Bits

Loading...

Loading...