Chapter 5

110 MIPS R4000 Microprocessor User's Manual

User Address Space Accesses: Access to the user address space is allowed

in any of the three operating modes.

Status Register Reset

The contents of the Status register are undefined at reset, except for the

following bits in the Diagnostic Status field:

• TS = 0

• ERL and BEV = 1

The SR bit distinguishes between the Reset exception and the Soft Reset

exception (caused either by Reset* or Nonmaskable Interrupt [NMI]).

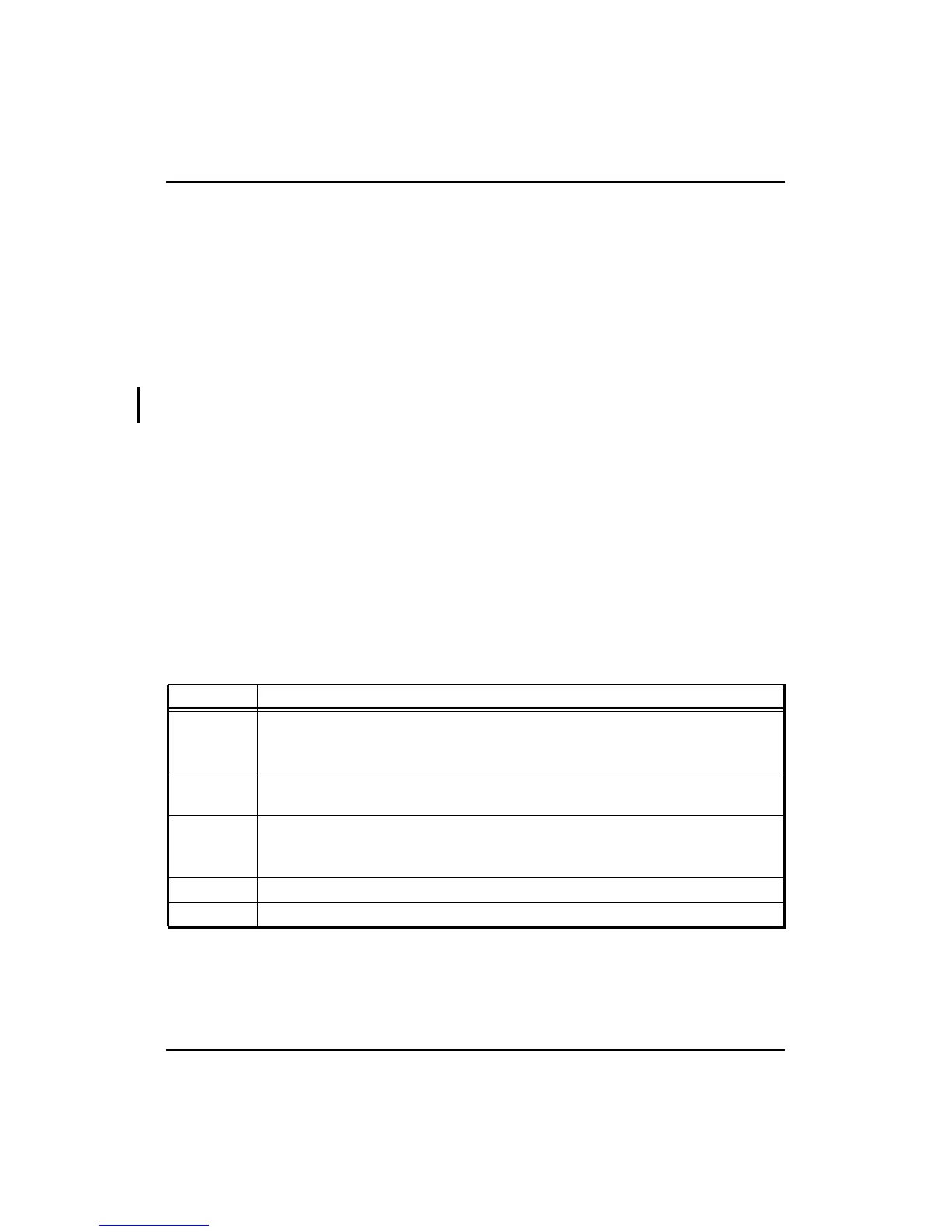

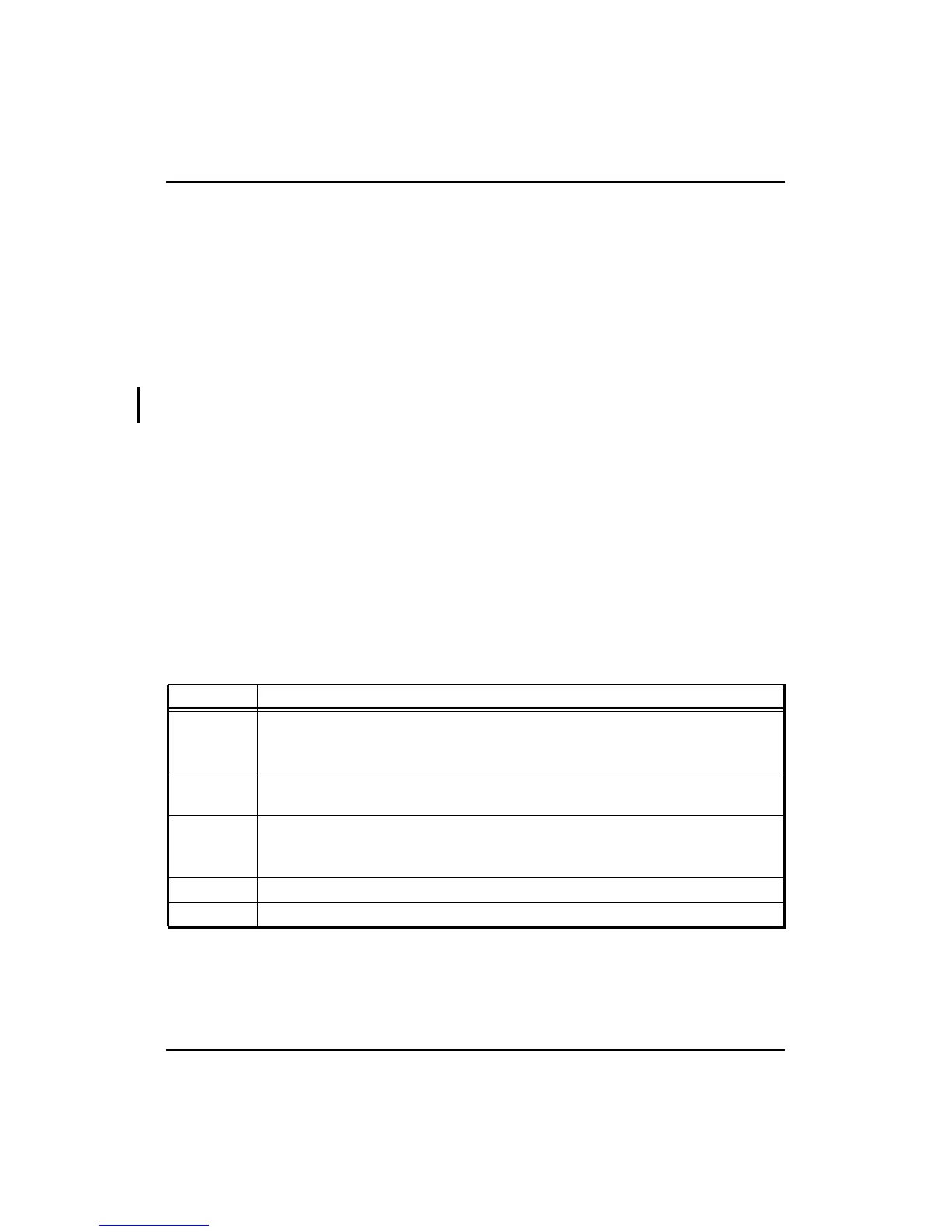

Cause Register (13)

The 32-bit read/write Cause register describes the cause of the most recent

exception.

Figure 5-7 shows the fields of this register; Table 5-5 describes the Cause

register fields. A 5-bit exception code (ExcCode) indicates one of the

causes, as listed in Table 5-6.

All bits in the Cause register, with the exception of the IP(1:0) bits, are read-

only; IP(1:0) are used for software interrupts.

Table 5-5 Cause Register Fields

Field Description

BD

Indicates whether the last exception taken occurred in a branch delay slot.

1 → delay slot

0 → normal

CE

Coprocessor unit number referenced when a Coprocessor Unusable

exception is taken.

IP

Indicates an interrupt is pending.

1 → interrupt pending

0 → no interrupt

ExcCode Exception code field (see Table 5-6)

0 Reserved. Must be written as zeroes, and returns zeroes when read.

Loading...

Loading...