Chapter 8

210 MIPS R4000 Microprocessor User's Manual

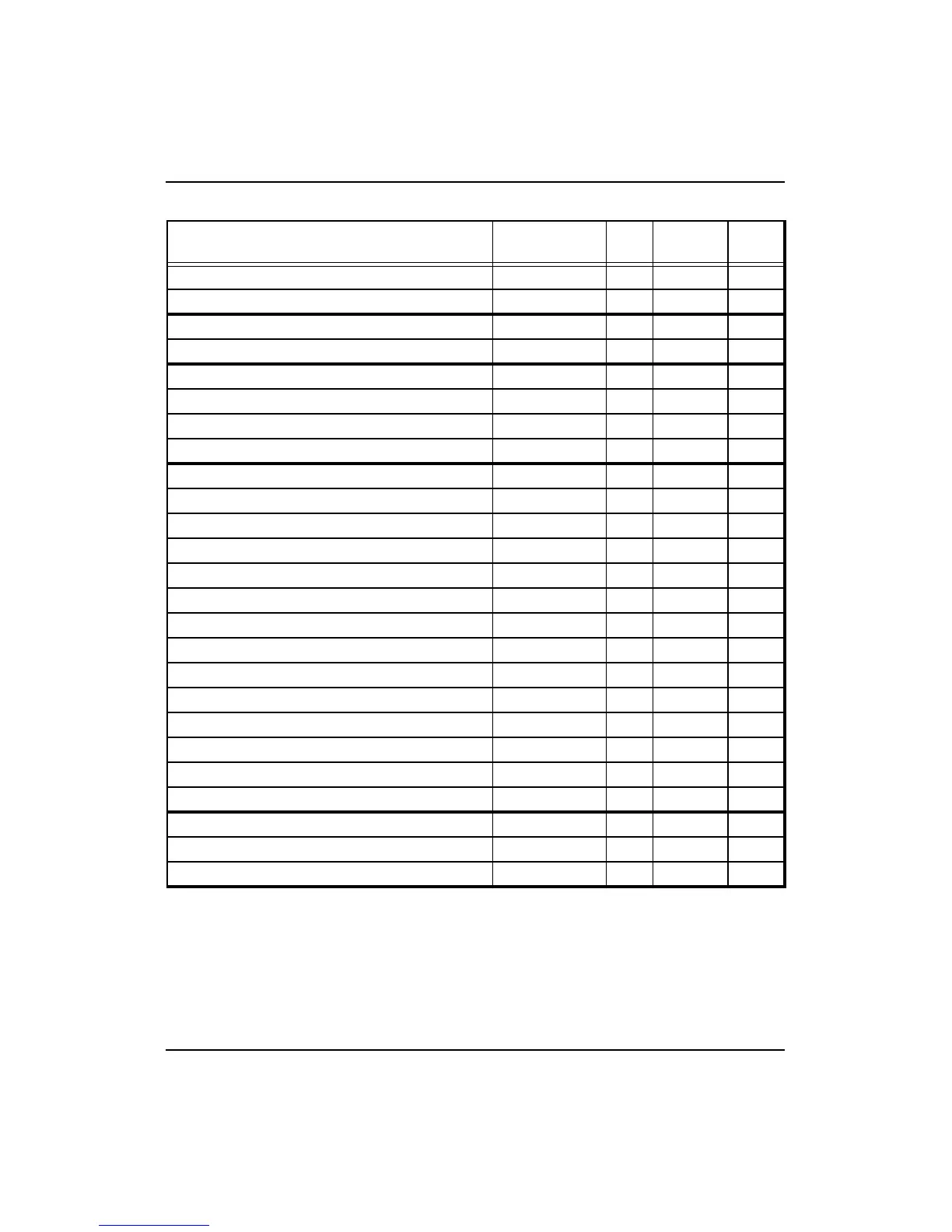

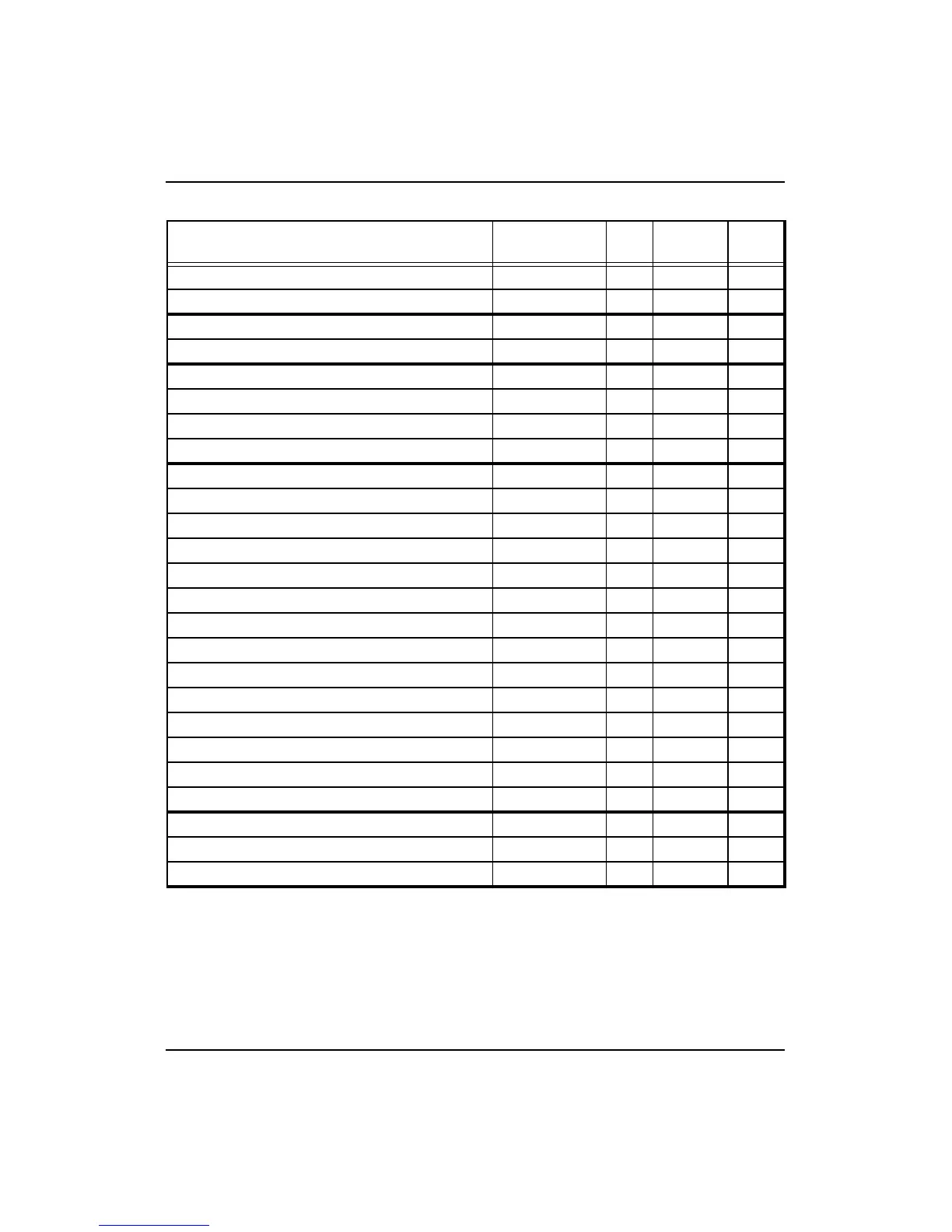

Table 8-7 (cont.) R4000SC/MC Processor Signal Summary

Description Name I/O

Asserted

State

3-State

Interrupt Int*(0) I Low No

Nonmaskable interrupt NMI* I Low No

Boot mode data in ModeIn I High No

Boot mode clock ModeClock O High No

JTAG data in JTDI I High No

JTAG data out JTDO O High No

JTAG command JTMS I High No

JTAG clock input JTCK I High No

Transmit clocks TClock(1:0) O High No

Receive clocks RClock(1:0) O High No

Master clock MasterClock I High No

Master clock out MasterOut O High No

Synchronization clock out SyncOut O High No

Synchronization clock in SyncIn I High No

I/O output IOOut O High No

I/O input IOIn I High No

Vcc is OK VCCOk I High No

Cold reset ColdReset* I Low No

Reset Reset* I Low No

Fault Fault* O Low No

Quiet Vcc for PLL VccP I High No

Quiet Vss for PLL VssP I High No

Status Status(7:0) O High No

Vcc sense VccSense I/O N/A No

Vss sense VssSense I/O N/A No

Loading...

Loading...