MIPS R4000 Microprocessor User's Manual 211

R4000 Processor Signal Descriptions

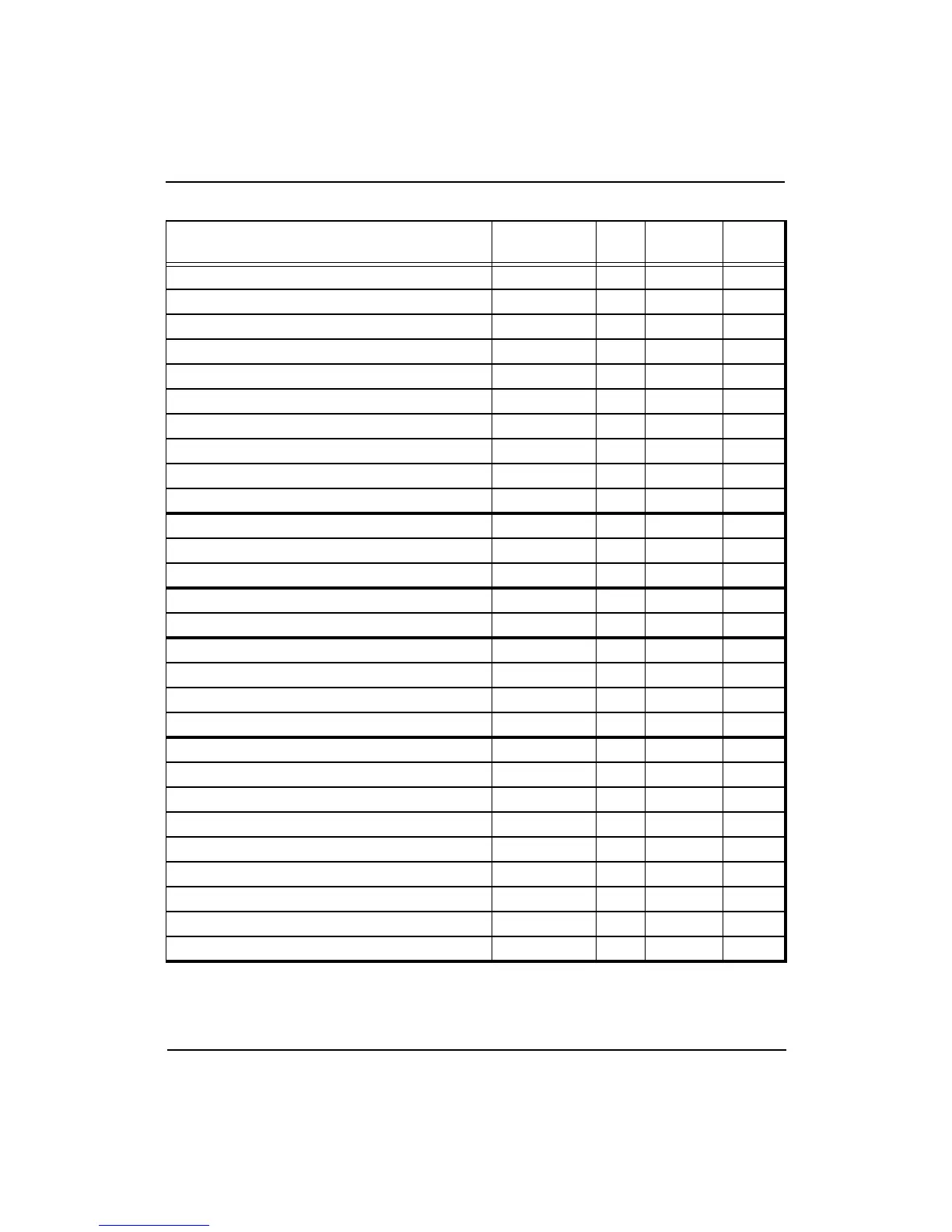

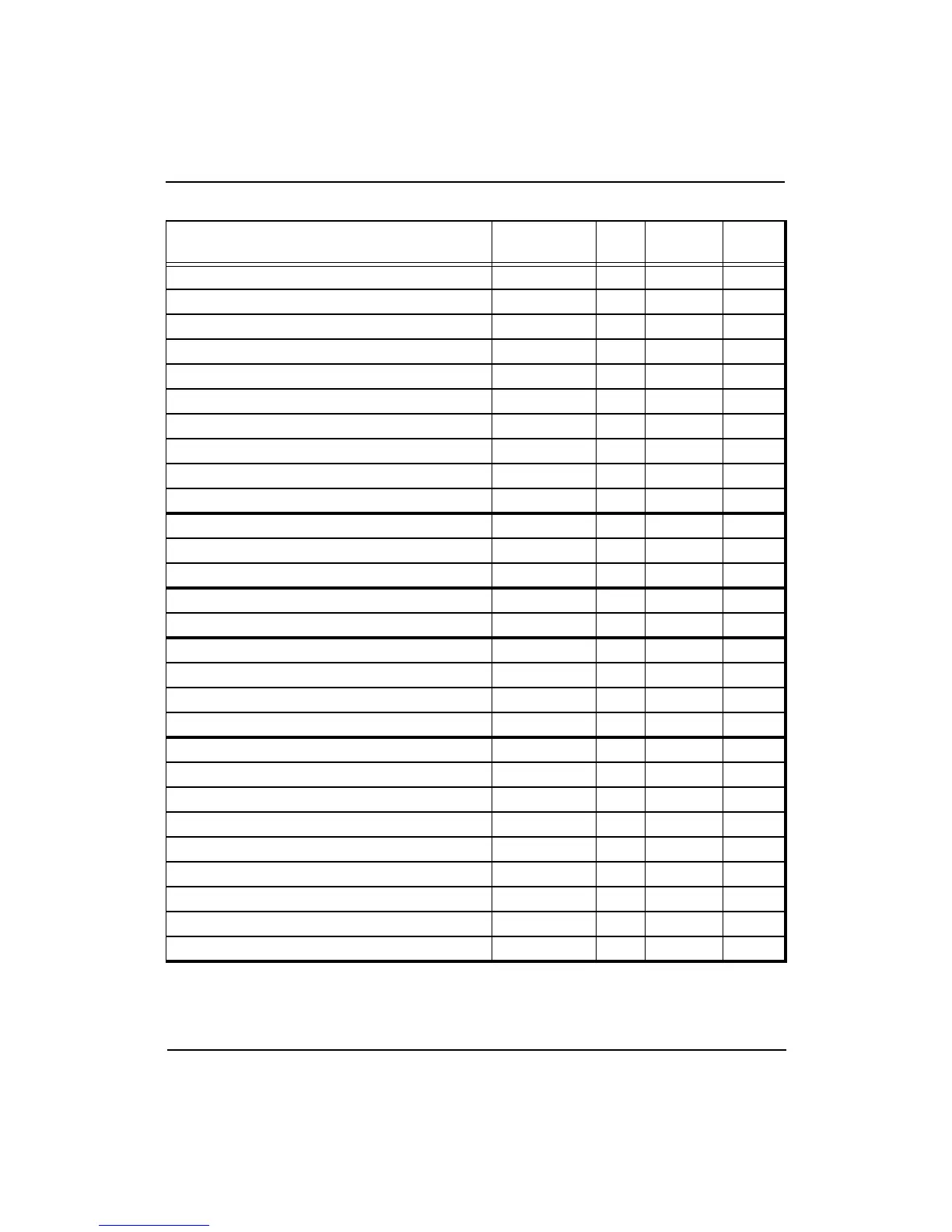

Table 8-8 R4000PC Processor Signal Summary

Description Name I/O

Asserted

State

3-State

System address/data bus SysAD(63:0) I/O High Yes

System address/data check bus SysADC(7:0) I/O High Yes

System command/data identifier bus SysCmd(8:0) I/O High Yes

System command/data identifier bus parity SysCmdP I/O High Yes

Valid input ValidIn* I Low No

Valid output ValidOut* O Low No

External request ExtRqst* I Low No

Release interface Release* O Low No

Read ready RdRdy* I Low No

Write ready WrRdy* I Low No

Interrupts Int*(5:1) I Low No

Interrupt Int*(0) I Low No

Nonmaskable interrupt NMI* I Low No

Boot mode data in ModeIn I High No

Boot mode clock ModeClock O High No

JTAG data in JTDI I High No

JTAG data out JTDO O High No

JTAG command JTMS I High No

JTAG clock input JTCK I High No

Transmit clocks TClock(1:0) O High No

Receive clocks RClock(1:0) O High No

Master clock MasterClock I High No

Master clock out MasterOut O High No

Synchronization clock out SyncOut O High No

Synchronization clock in SyncIn I High No

I/O output IOOut O High No

I/O input IOIn I High No

Vcc is OK VCCOk I High No

Loading...

Loading...