Chapter 5

106 MIPS R4000 Microprocessor User's Manual

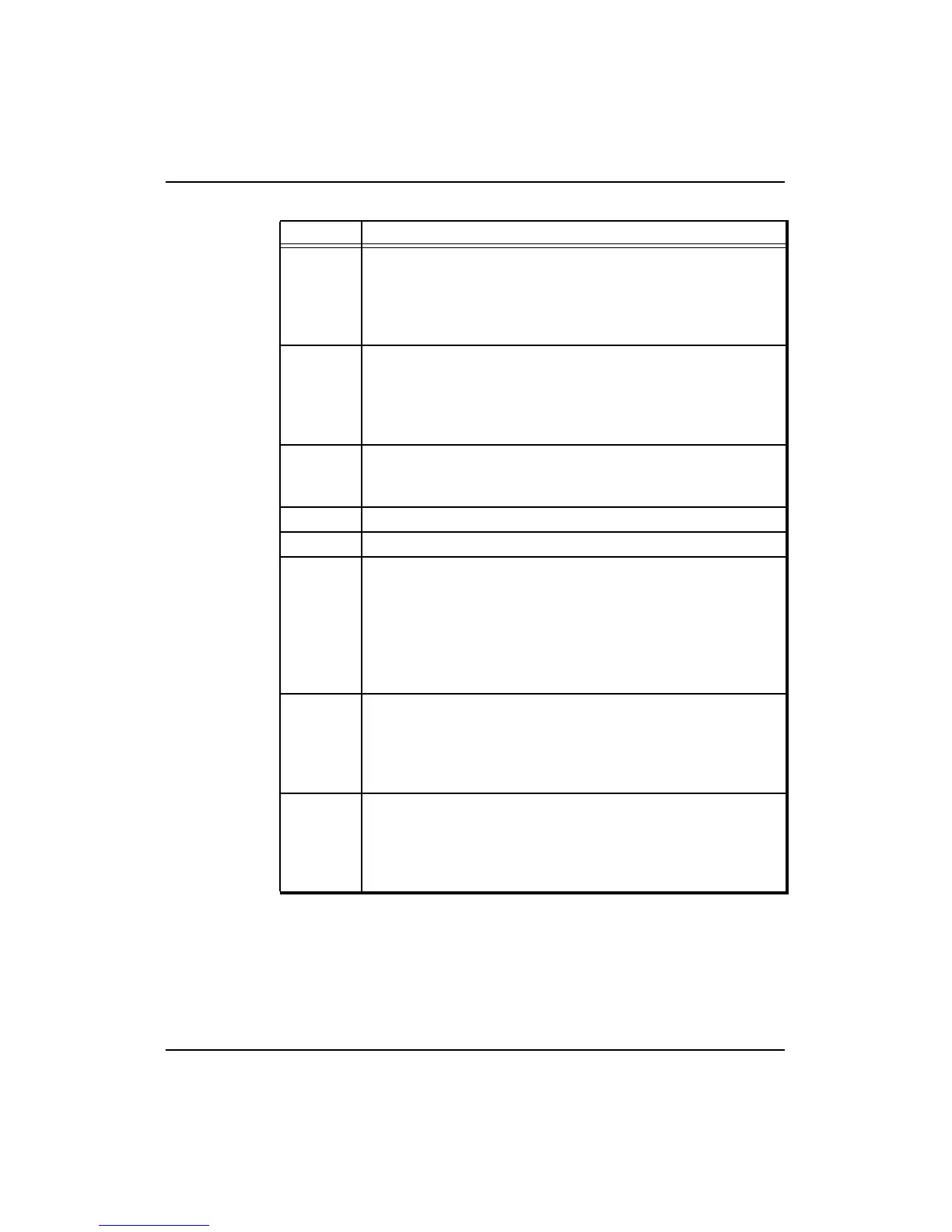

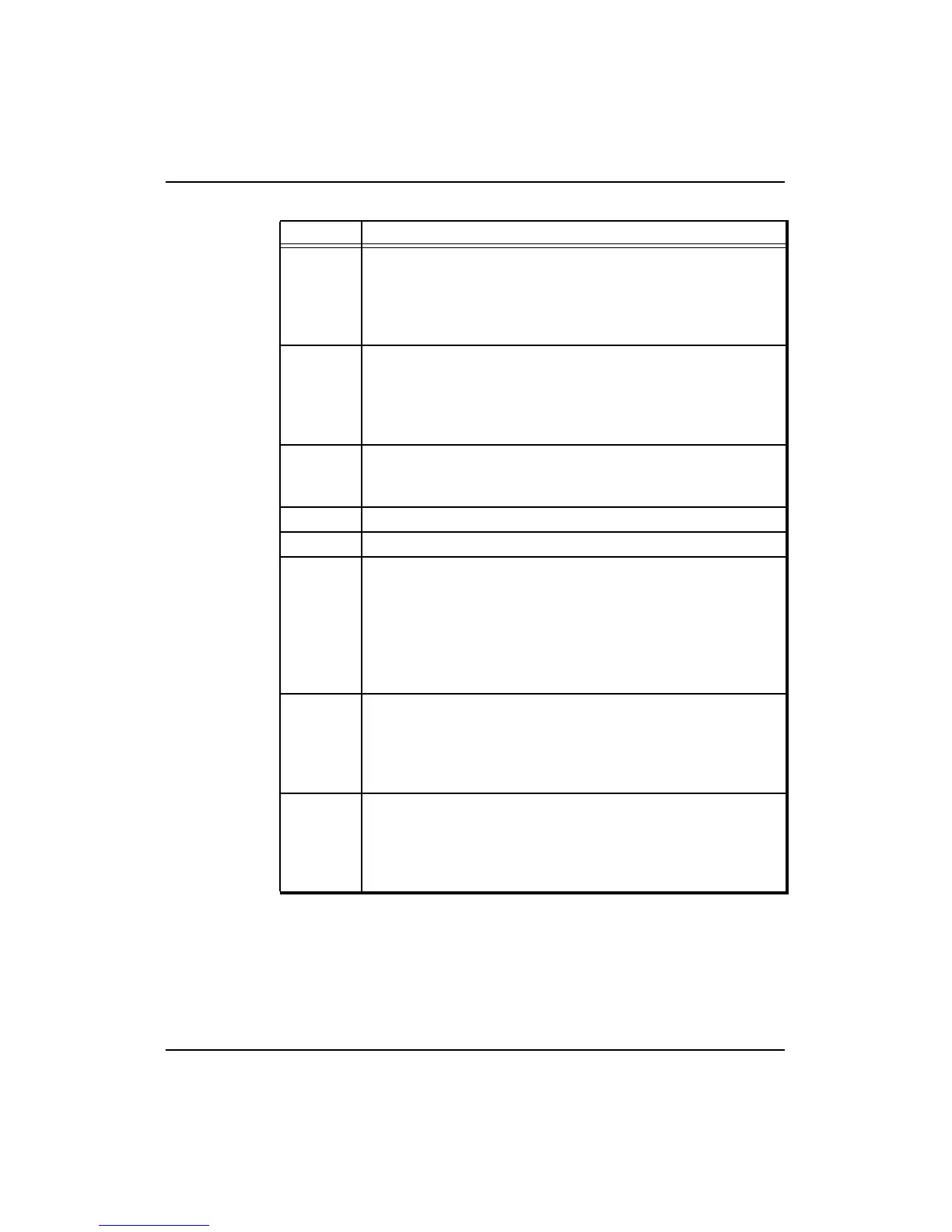

Table 5-3 Status Register Fields

Field Description

CU

Controls the usability of each of the four coprocessor unit

numbers. CP0 is always usable when in Kernel mode,

regardless of the setting of the CU

0

bit.

1 → usable

0 → unusable

RP

Enables reduced-power operation by reducing the internal

clock frequency. The clock divisor is programmable at boot

time.

0 → full speed

1→ reduced clock

FR

Enables additional floating-point registers

0 → 16 registers

1 → 32 registers

RE Reverse-Endian bit, valid in User mode.

DS Diagnostic Status field (see Figure 5-6).

IM

Interrupt Mask: controls the enabling of each of the external,

internal, and software interrupts. An interrupt is taken if

interrupts are enabled, and the corresponding bits are set in

both the Interrupt Mask field of the Status register and the

Interrupt Pending field of the Cause register.

0 → disabled

1→ enabled

KX

Enables 64-bit addressing in Kernel mode. The extended-

addressing TLB refill exception is used for TLB misses on

kernel addresses.

0 → 32−bit

1 → 64−bit

SX

Enables 64-bit addressing and operations in Supervisor

mode. The extended-addressing TLB refill exception is used

for TLB misses on supervisor addresses.

0 → 32−bit

1 → 64−bit

Loading...

Loading...