Chapter 1

16 MIPS R4000 Microprocessor User's Manual

Tables 1-2 through 1-17 list CPU instructions common to MIPS R-Series

processors, along with those instructions that are extensions to the

instruction set architecture. The extensions result in code space

reductions, multiprocessor support, and improved performance in

operating system kernel code sequences—for instance, in situations where

run-time bounds-checking is frequently performed. Table 1-18 lists CP0

instructions.

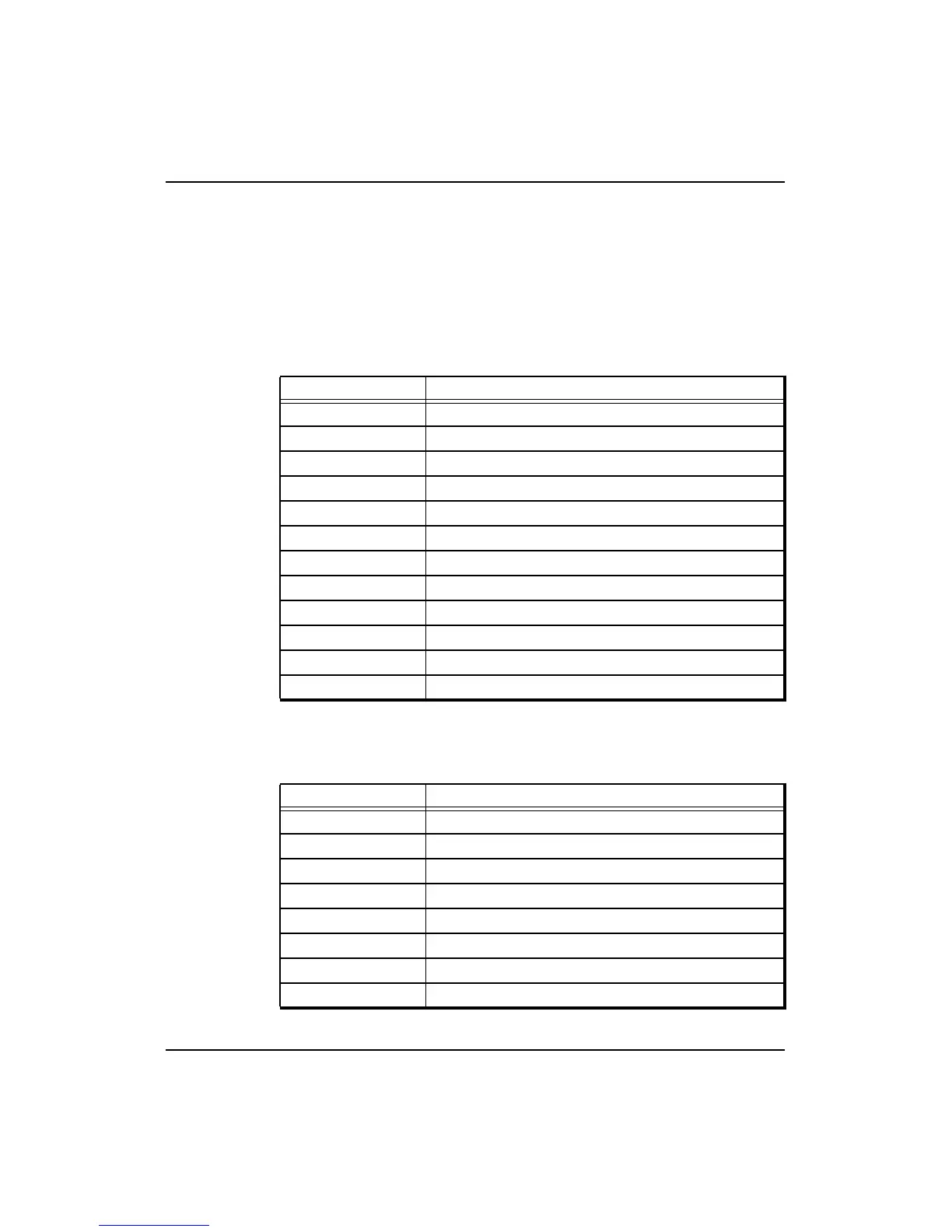

Table 1-2 CPU Instruction Set: Load and Store Instructions

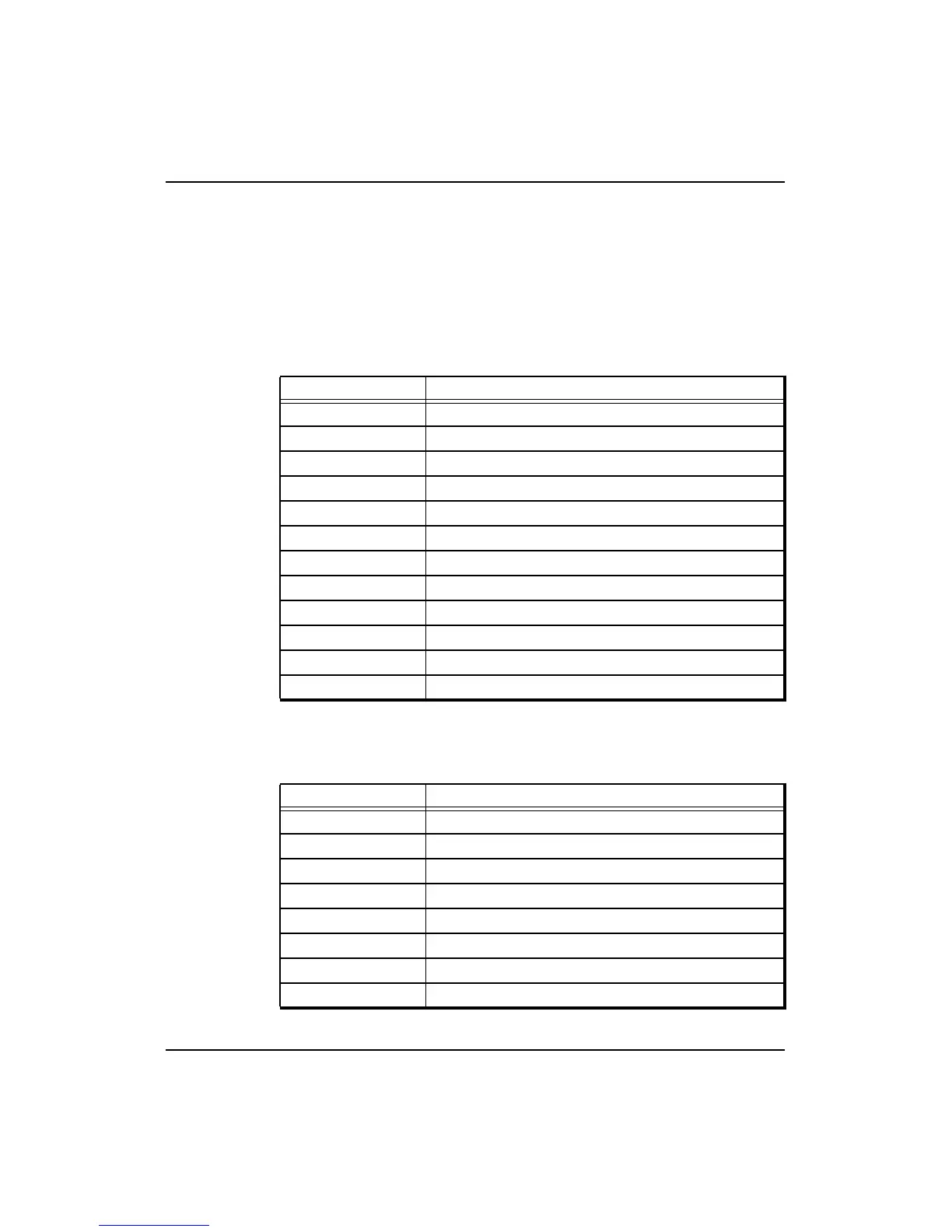

Table 1-3 CPU Instruction Set: Arithmetic Instructions (ALU Immediate)

OpCode Description

LB Load Byte

LBU Load Byte Unsigned

LH Load Halfword

LHU Load Halfword Unsigned

LW Load Word

LWL Load Word Left

LWR Load Word Right

SB Store Byte

SH Store Halfword

SW Store Word

SWL Store Word Left

SWR Store Word Right

OpCode Description

ADDI Add Immediate

ADDIU Add Immediate Unsigned

SLTI Set on Less Than Immediate

SLTIU Set on Less Than Immediate Unsigned

ANDI AND Immediate

ORI OR Immediate

XORI Exclusive OR Immediate

LUI Load Upper Immediate

Loading...

Loading...