Appendix A

A-120 MIPS R4000 Microprocessor User's Manual

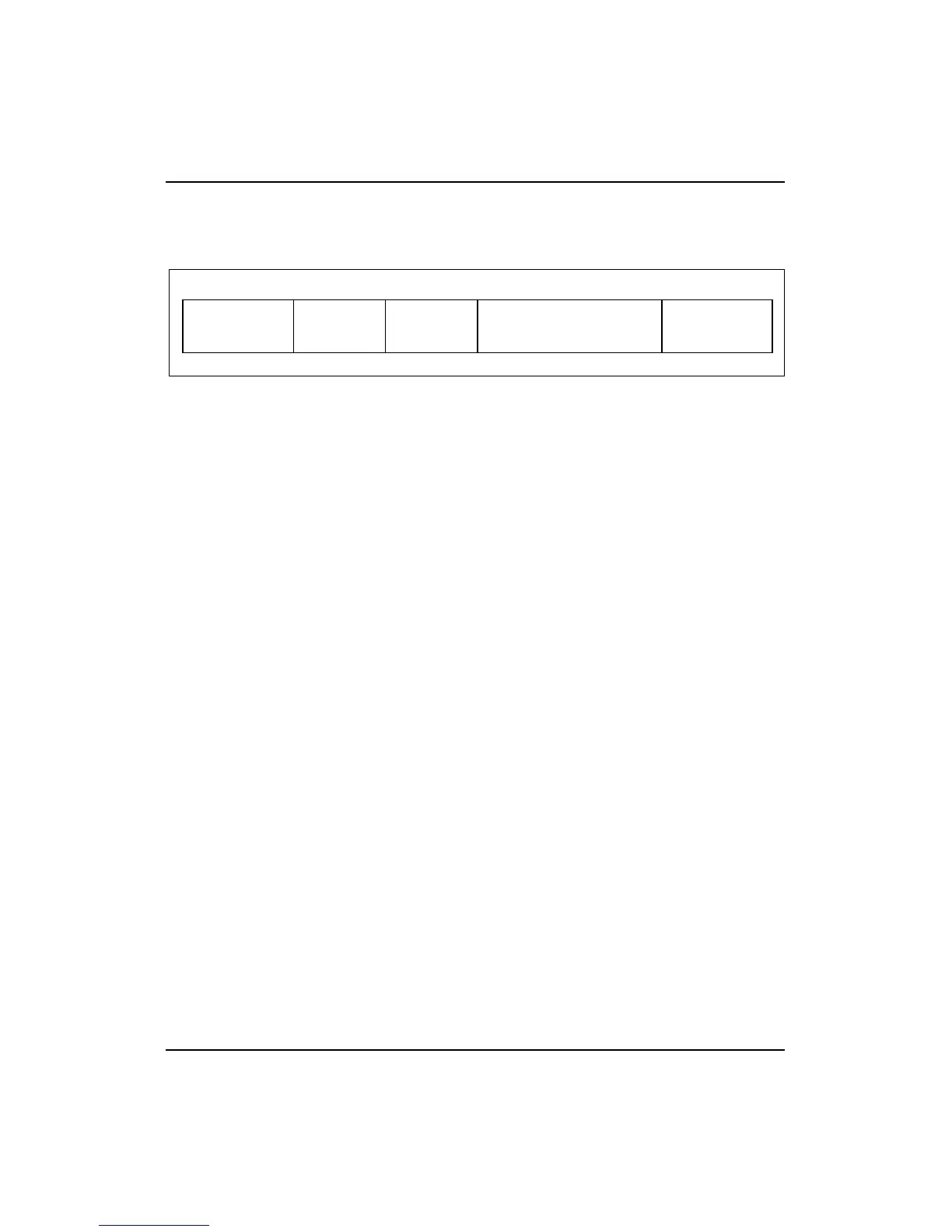

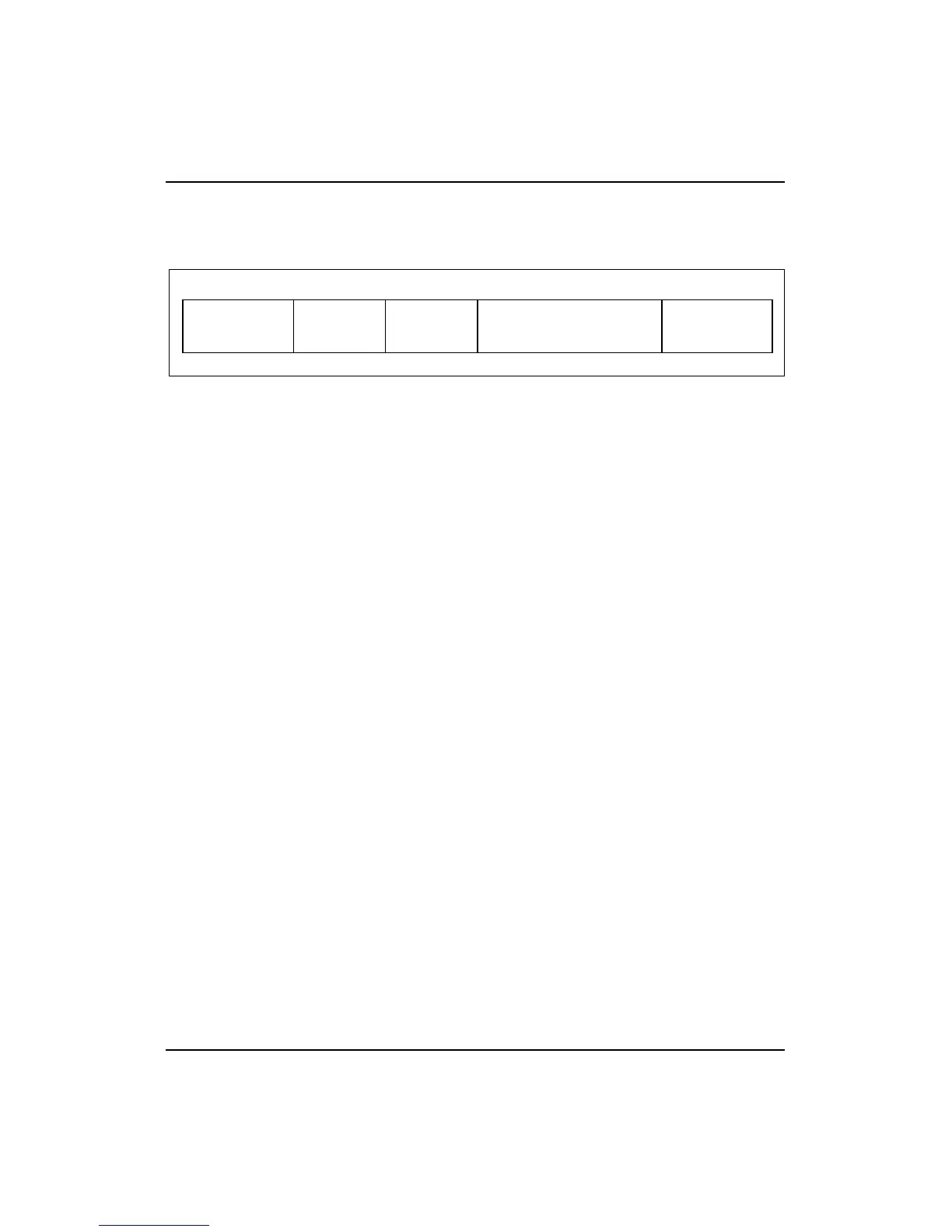

Format:

MULTU rs, rt

Description:

The contents of general register rs and the contents of general register rt

are multiplied, treating both operands as unsigned values. No overflow

exception occurs under any circumstances. In 64-bit mode, the operands

must be valid 32-bit, sign-extended values.

When the operation completes, the low-order word of the double result is

loaded into special register LO, and the high-order word of the double

result is loaded into special register HI.

If either of the two preceding instructions is MFHI or MFLO, the results of

these instructions are undefined. Correct operation requires separating

reads of HI or LO from writes by a minimum of two instructions.

MULTU

Multiply Unsigned

31 2526 2021 1516 0

rs rt

655

65

10 6

SPECIAL 0 MULTU

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1

MULTU

Loading...

Loading...