Appendix A

A-172 MIPS R4000 Microprocessor User's Manual

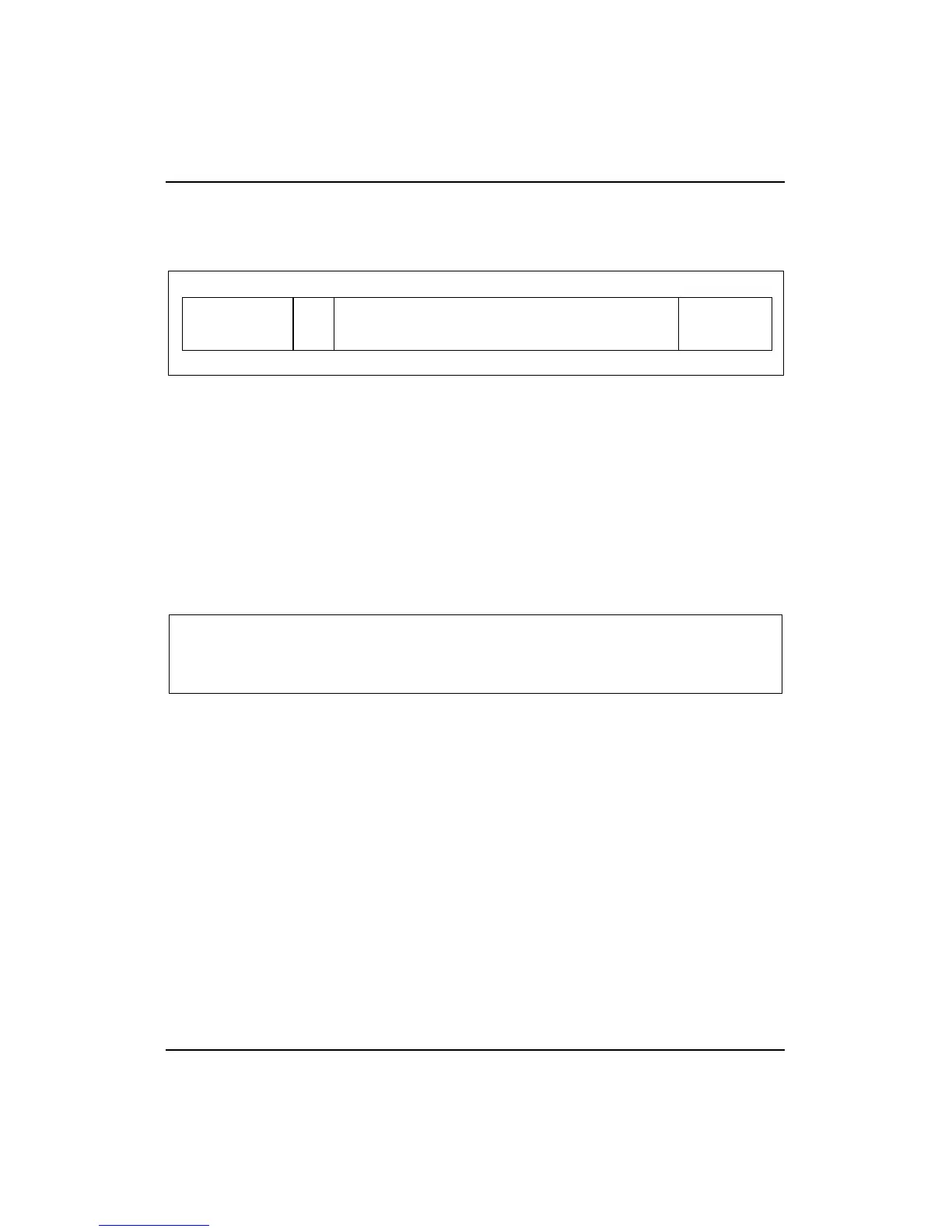

Format:

TLBWR

Description:

The G bit of the TLB is written with the logical AND of the G bits in the

EntryLo0 and EntryLo1 registers.

The TLB entry pointed at by the contents of the TLB Random register is

loaded with the contents of the EntryHi and EntryLo registers.

Operation:

Exceptions:

Coprocessor unusable exception

TLBWR

Write Random TLB Entry

0

6

6 531 25 2426

COP0

6

0

TLBWR

191

CO

0 1 0 0 0 0 0 0 0 1 1 00 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 01

TLBWR

32, 64T: TLB[Random

5...0

] ←

PageMask || (EntryHi and not PageMask) || EntryLo1 || EntryLo0

Loading...

Loading...