Chapter 4

68 MIPS R4000 Microprocessor User's Manual

The User segment starts at address 0 and the current active user process

resides in either useg (in 32-bit mode) or xuseg (in 64-bit mode). The TLB

identically maps all references to useg/xuseg from all modes, and controls

cache accessibility.

†

The processor operates in User mode when the Status register contains the

following bit-values:

• KSU bits = 10

2

• EXL = 0

• ERL = 0

In conjunction with these bits, the UX bit in the Status register selects

between 32- or 64-bit User mode addressing as follows:

• when UX = 0, 32-bit useg space is selected and TLB misses are

handled by the 32-bit TLB refill exception handler

• when UX = 1, 64-bit xuseg space is selected and TLB misses are

handled by the 64-bit XTLB refill exception handler

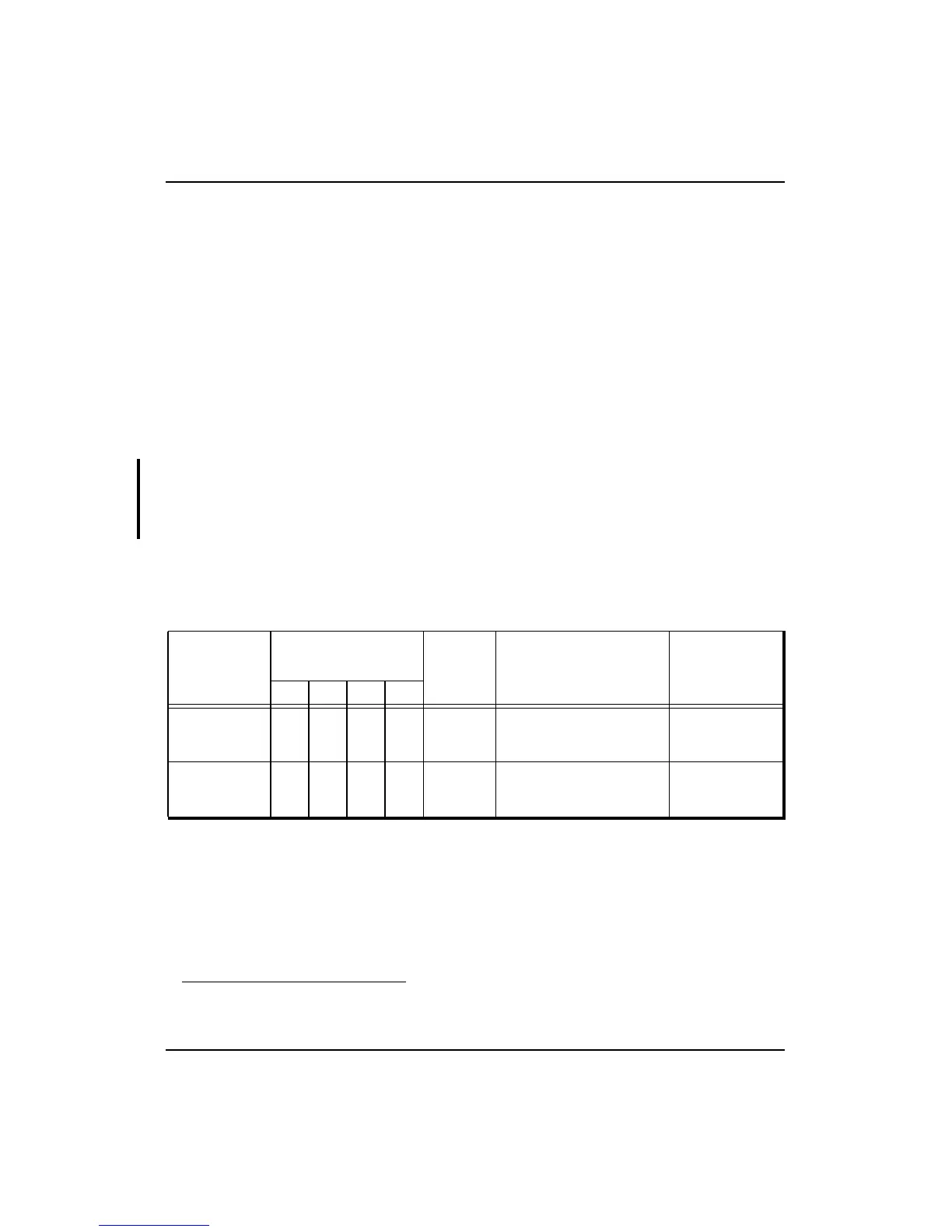

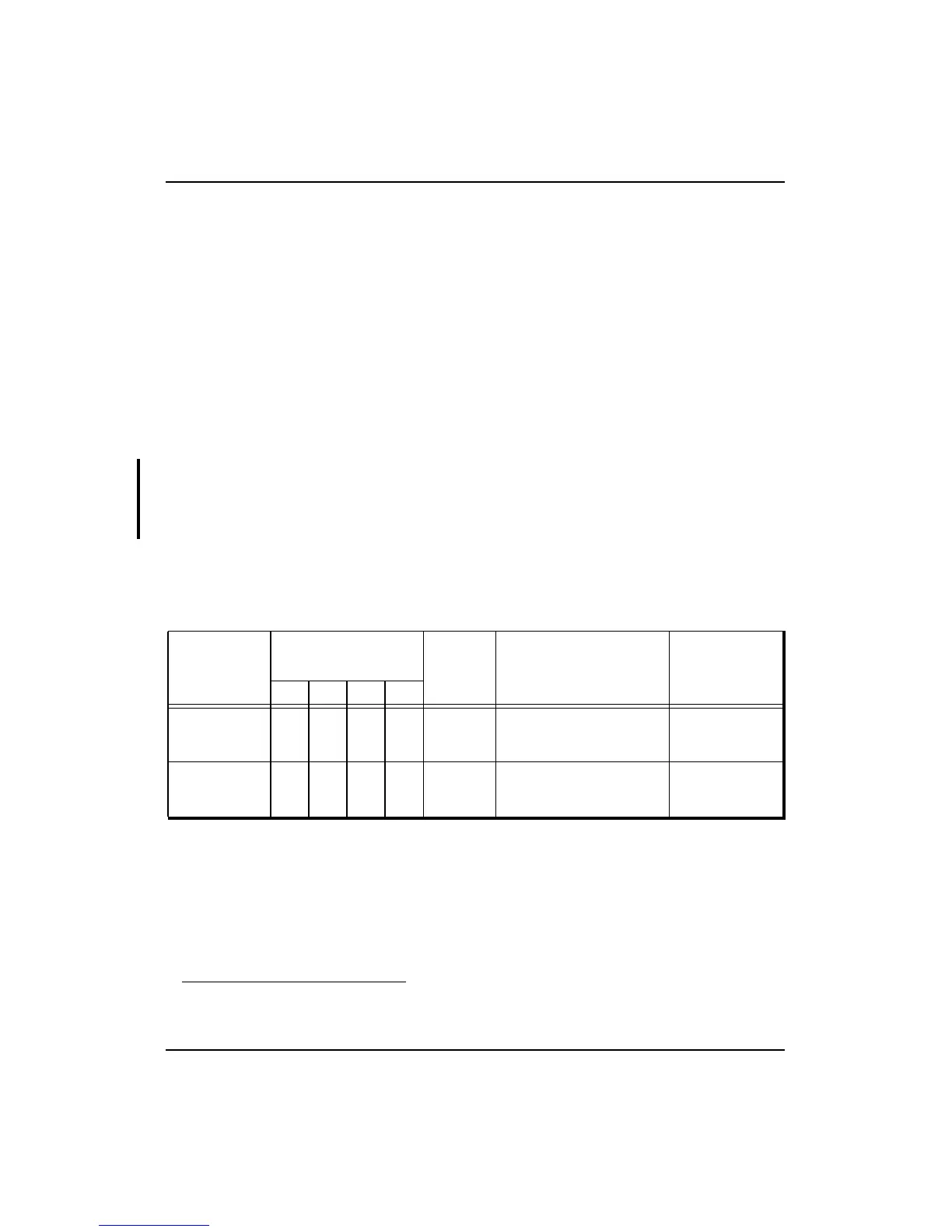

Table 4-1 lists the characteristics of the two user mode segments, useg and

xuseg.

Table 4-1 32-bit and 64-bit User Mode Segments

† The cached (C) field in a TLB entry determines whether the reference is cached; see Figure

4-8.

Address Bit

Values

Status Register

Segment

Name

Address Range Segment SizeBit Values

KSU EXL ERL UX

32-bit

A(31) = 0

10

2

000useg

0x0000 0000

through

0x7FFF FFFF

2 Gbyte

(2

31

bytes)

64-bit

A(63:40) = 0

10

2

001xuseg

0x0000 0000 0000 0000

through

0x0000 00FF FFFF FFFF

1 Tbyte

(2

40

bytes)

Loading...

Loading...