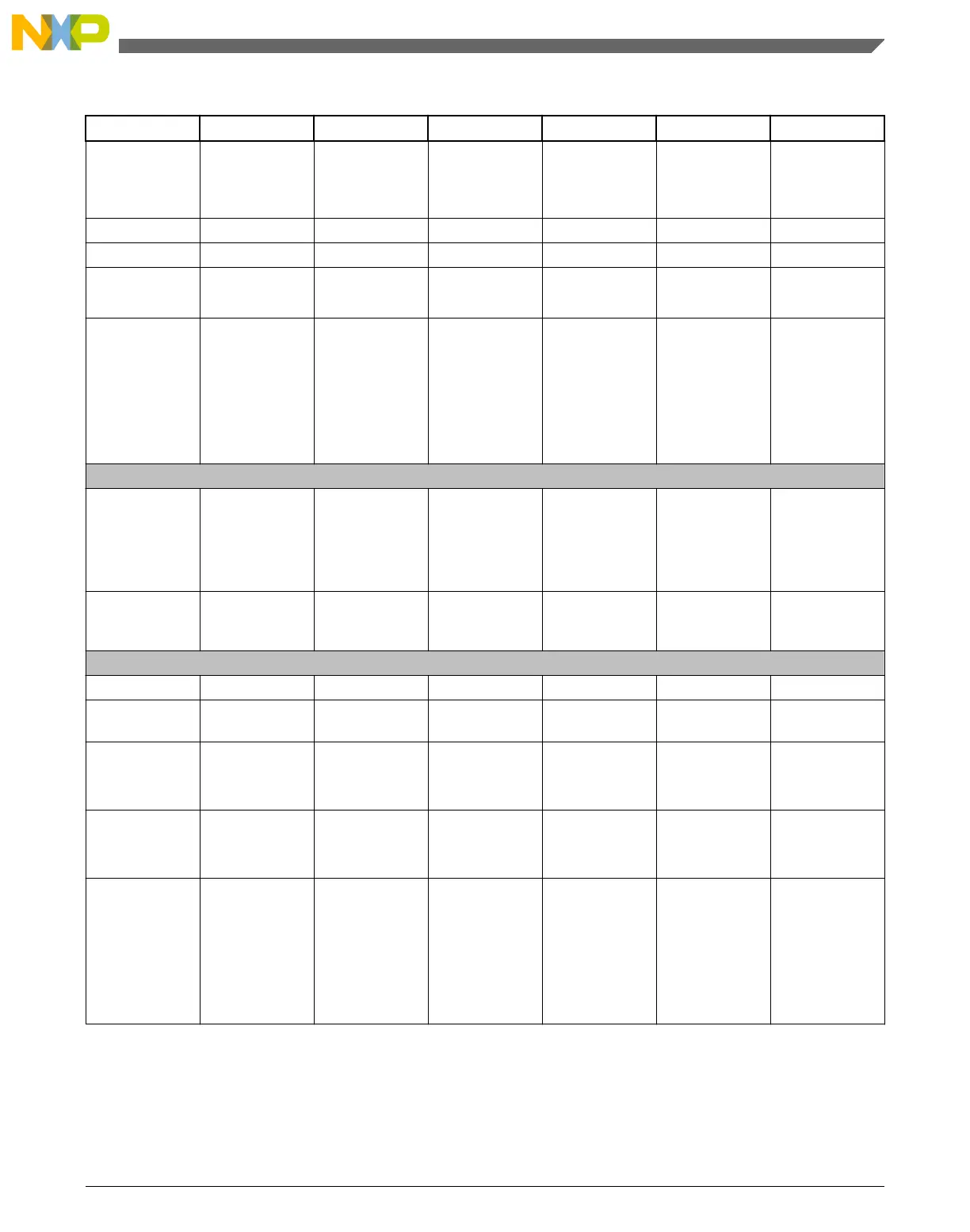

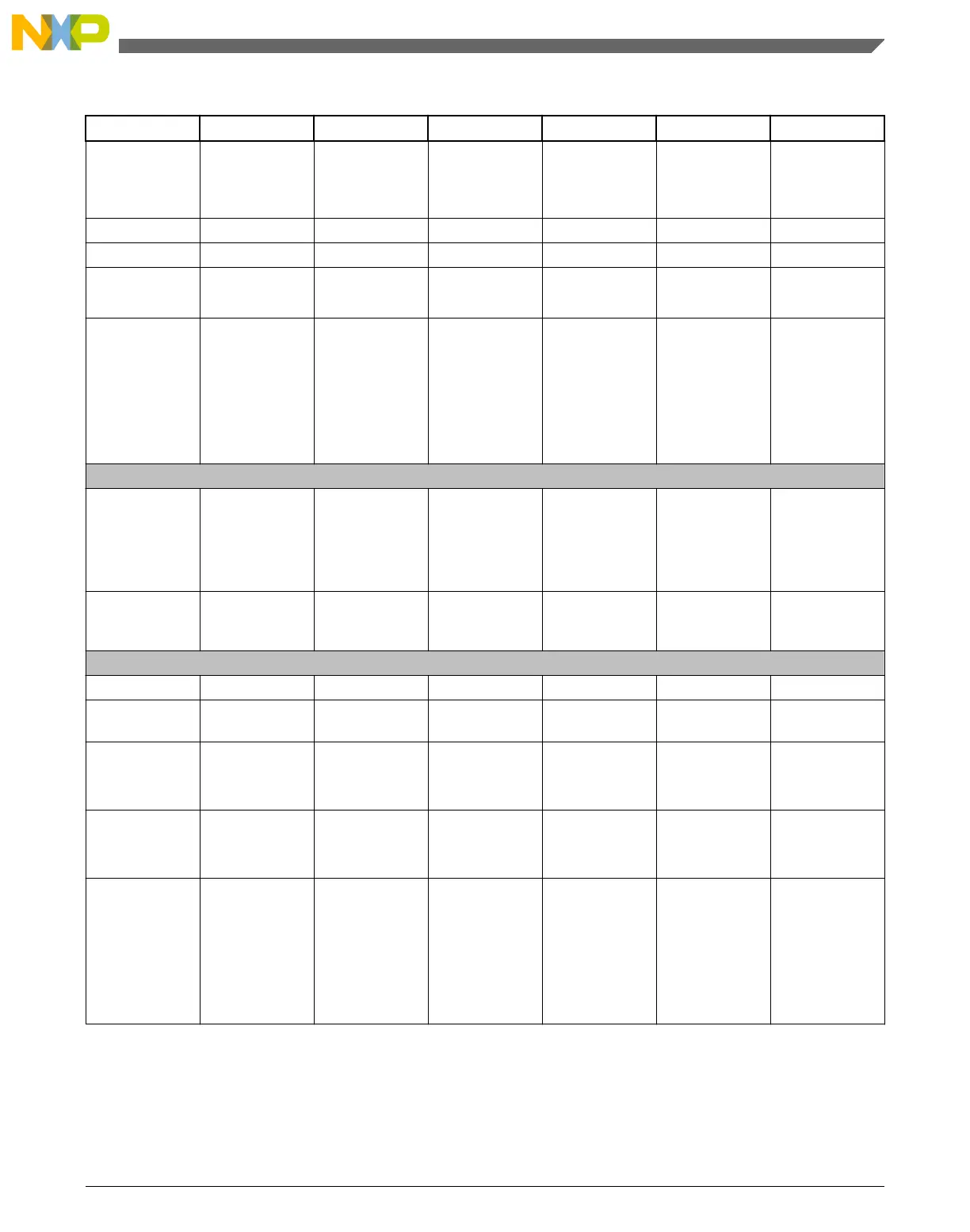

Table 7-2. Module operation in low power modes (continued)

Modules VLPR VLPW Stop VLPS LLS VLLSx

MCG 4 MHz IRC 4 MHz IRC static -

MCGIRCLK

optional; PLL

optional

static -

MCGIRCLK

optional

static - no clock

output

OFF

Core clock 4 MHz max OFF OFF OFF OFF OFF

Platform clock 4 MHz max 4 MHz max OFF OFF OFF OFF

System clock 4 MHz max

OFF in CPO

4 MHz max OFF OFF OFF OFF

Bus clock 1 MHz max

OFF in CPO

1 MHz max OFF

24 MHz max in

PSTOP2 from

RUN

1 MHz max in

PSTOP2 from

VLPR

OFF OFF OFF

Memory and memory interfaces

Flash 1 MHz max

access - no

program

No register

access in CPO

low power low power low power OFF OFF

SRAM_U and

SRAM_L

low power low power low power low power low power low power in

VLLS3, OFF in

VLLS0/1

Communication interfaces

USB FS/LS static static static static static OFF

USB Voltage

Regulator

optional optional optional optional optional optional

UART0 1 Mbps

Async operation

in CPO

1 Mbps Async operation

FF in PSTOP2

Async operation static OFF

UART1 , UART2 62.5 kbps

static, wakeup

on edge in CPO

62.5 kbps static, wakeup

on edge

FF in PSTOP2

static, wakeup

on edge

static OFF

SPI0 master mode

500 kbps,

slave mode 250

kbps

static, slave

mode receive in

CPO

master mode

500 kbps,

slave mode 250

kbps

static, slave

mode receive

FF in PSTOP2

static, slave

mode receive

static OFF

Table continues on the next page...

Chapter 7 Power Management

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 145

Loading...

Loading...