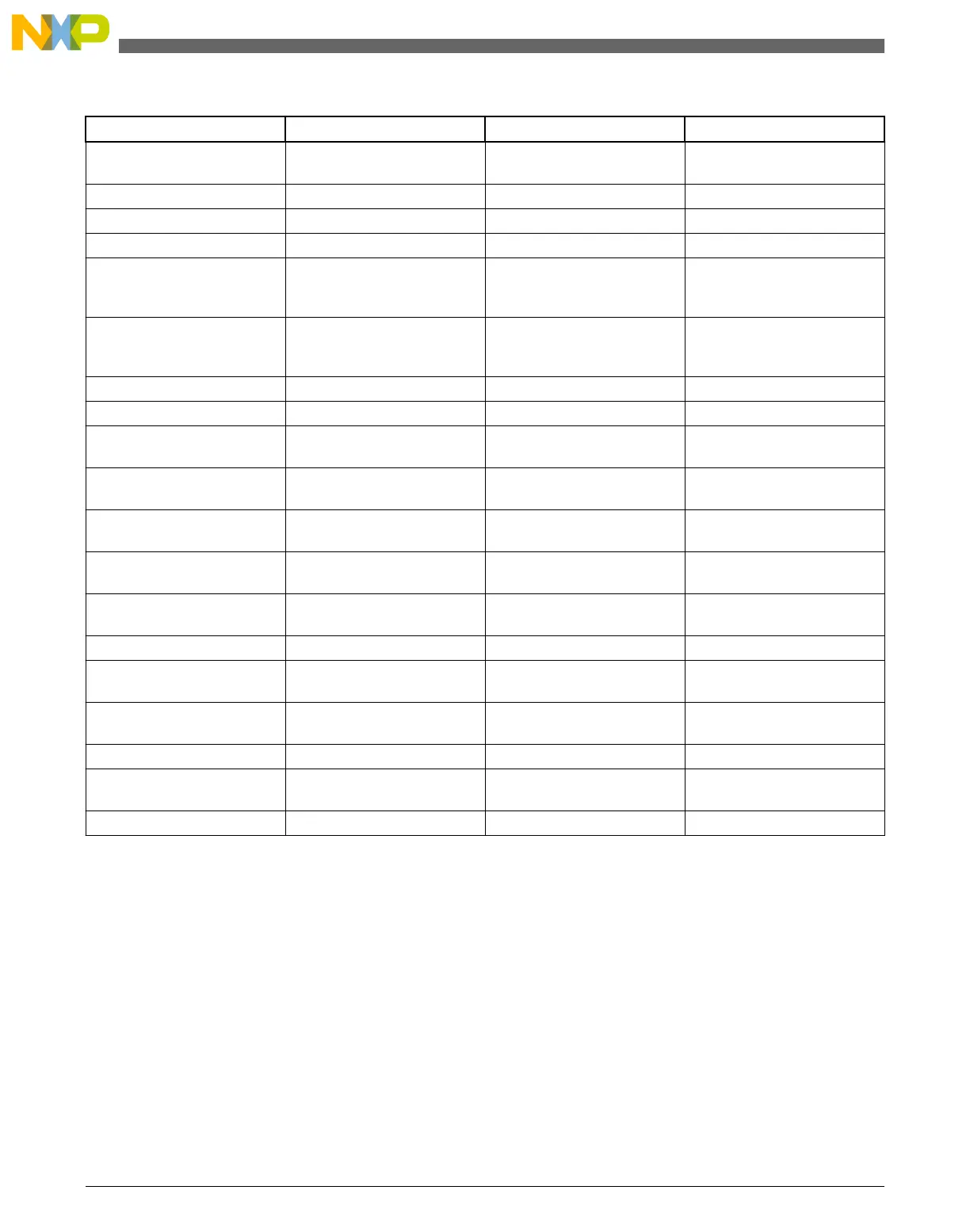

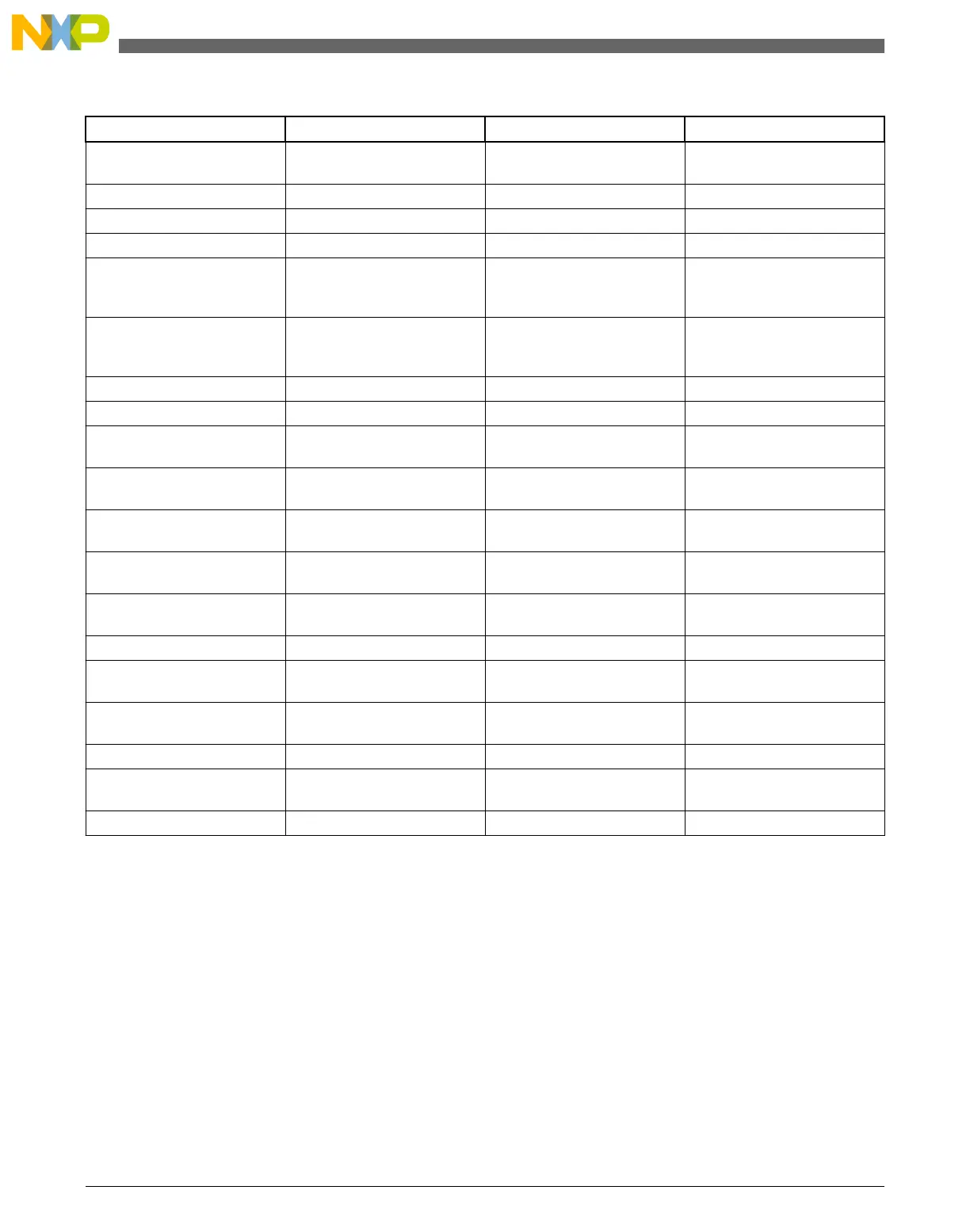

Table 3-4. Table 3. ARM Cortex-M0+ parameter settings (continued)

Parameter Verilog Name Value Description

Endianess BE 0 Little endian control for data

transfers

Breakpoints BKPT 2 Implements 2 breakpoints

Debug Support DBG 1 = Present

Halt Event Support HALTEV 1 = Present

I/O Port IOP 1 = Present Implements single-cycle ld/st

accesses to special addr

space

IRQ Mask Enable IRQDIS 0x00000000 Assume (for now) all 32 IRQs

are used (set if IRQ is

disabled)

Debug Port Protocol JTAGnSW 0 = SWD SWD protocol, not JTAG

Core Memory Protection MPU 0 = Absent No MPU

Number of IRQs NUMIRQ 32 Assume full NVIC request

vector

Reset all regs RAR 0 = Standard Do not force all registers to be

async reset

Multiplier SMUL 0 = Fast Mul Implements single-cycle

multiplier

Multi-drop Support SWMD 0 = Absent Do not include serial wire

support for multi-drop

System Tick Timer SYST 1 = Present Implements system tick timer

(for CM4 compatibility)

DAP Target ID TARGETID 0

User/Privileged USER 1 = Present Implements processor

operating modes

Vector Table Offset Register VTOR 1 = Present Implements relocation of

exception vector table

WIC Support WIC 1 = Present Implements WIC interface

WIC Requests WICLINES 34 Exact number of wakeup

IRQs is 34

Watchpoints WPT 2 Implements 2 watchpoints

For details on the ARM Cortex-M0+ processor core see the ARM website: arm.com.

3.3.1.2 Buses, Interconnects, and Interfaces

The ARM Cortex-M0+ core has two bus interfaces:

• single 32-bit AMBA-3 AHB-Lite system interface that provides connections to

peripherals and all system memory, which includes flash and RAM.

• single 32-bit I/O port bus interfacing to the GPIO with 1-cycle loads and stores.

Core Modules

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

50 Freescale Semiconductor, Inc.

Loading...

Loading...