Programmer’s Guide BCM5722

10/15/07

Broadcom Corporation

Document 5722-PG101-R Configuration Space Page 110

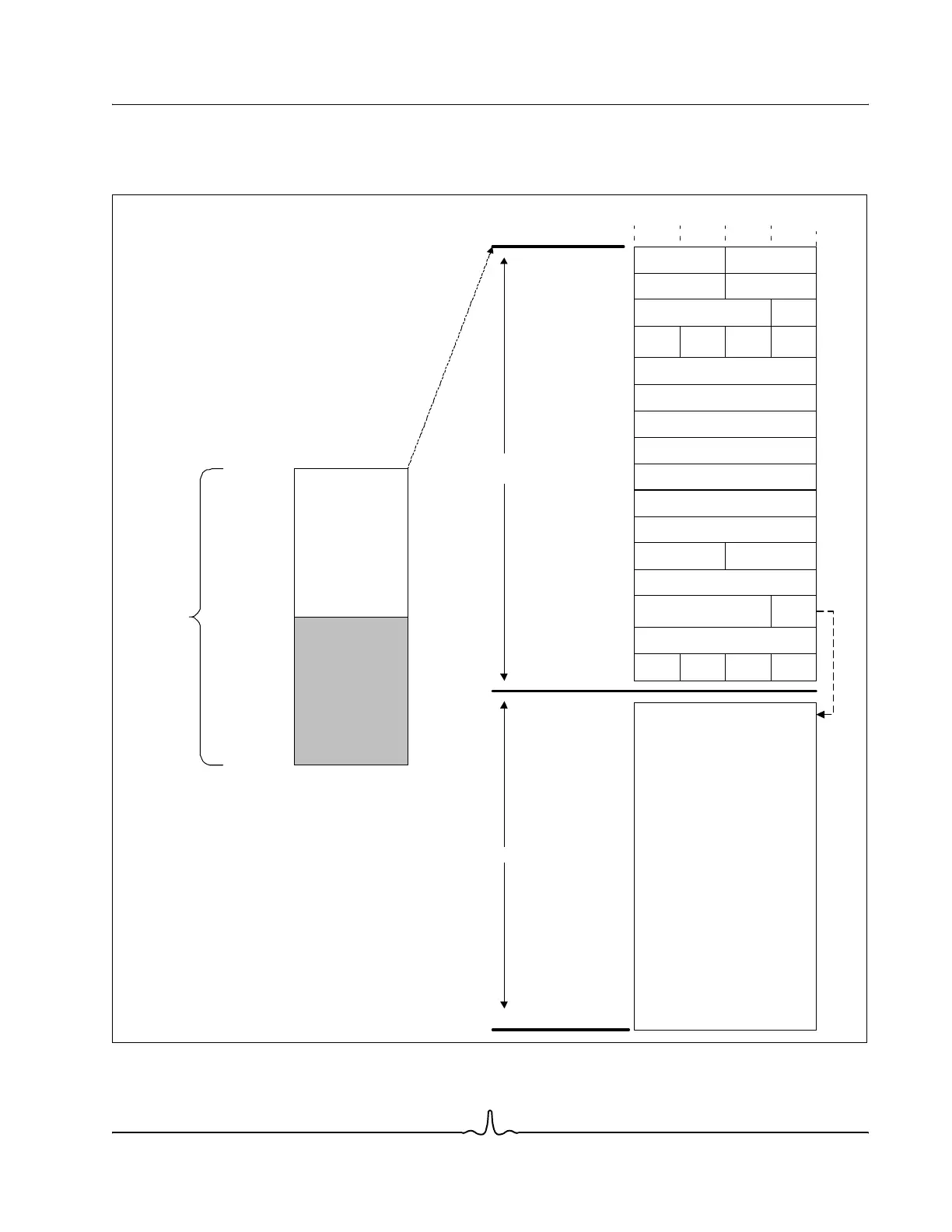

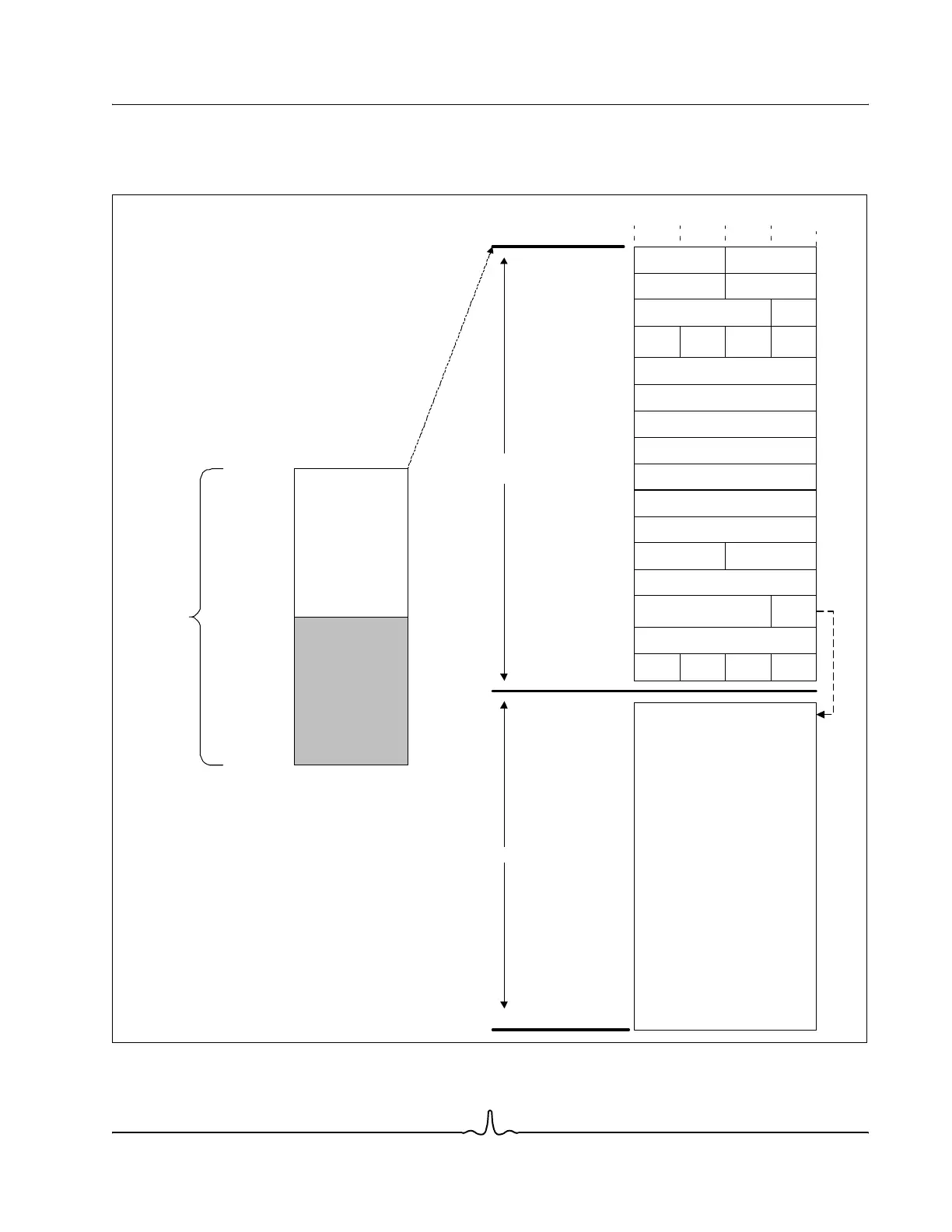

The header region (see Figure 39) is required by the PCI 2.2 specification. These registers must be implemented. The

capabilities registers are optional; however, they must adhere to section 6.7 of the PCI SIIG 2.2 specification. Each capability

has a unique ID, which is well-defined. The capabilities are chained using the Next Caps field, in the capability register. The

last capability will have a Next Caps field, which is zeroed.

Figure 39: Header Region Registers

See the PCI configuration registers in Section 12: “BCM5722 Ethernet Controller Register Definitions” on page 186.

Device ID

(0x14E4)

0x00

Vendor ID

0x04

Status

Register

0x08

Class Code Rev ID

0x0C

0x10

Cache

Line

Size

0x14

BAR 1 (Lower 32 bits)

Bytes

Command

Register

00010203

Latency

Timer

Hdr

Type

BIST

BAR 2 (Upper 32 bits)

BAR 3

Not Implemented

BAR 4

Not Implemented

0x18

0x1C

SubSystem

Vendor ID

SubSystem

ID

Expansion ROM

BAR

0x20

0x24

BAR 5

Not Implemented

BAR 6

Not Implemented

Reserved

0x28

0x2C

0x30

Caps

Ptr

(0x48)

Reserved

Int

Line

Int

Pin

Min

Gnt

Max

Lat

0x34

0x38

Reserved

0x3C

0x40

Capabilities

Required

0x64

Header Region

0x00

Capabilities

0xFF

PCI

Configuration

Registers

255

ytes

Loading...

Loading...