BCM5722 Programmer’s Guide

10/15/07

Broadcom Corporation

Page 409 PCIe Registers Document 5722-PG101-R

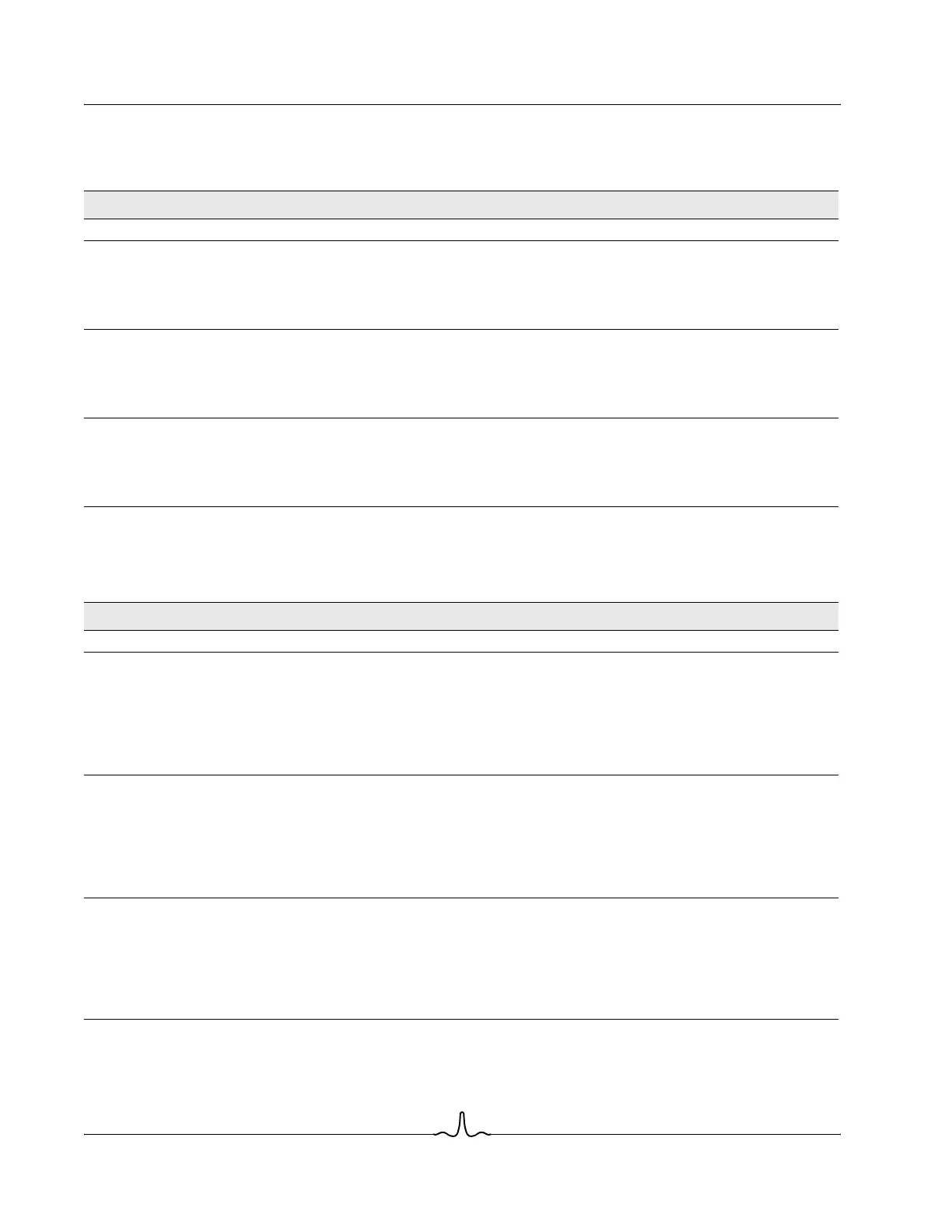

PHY RECEIVE ERROR THRESHOLD REGISTER (OFFSET 0X7E28)

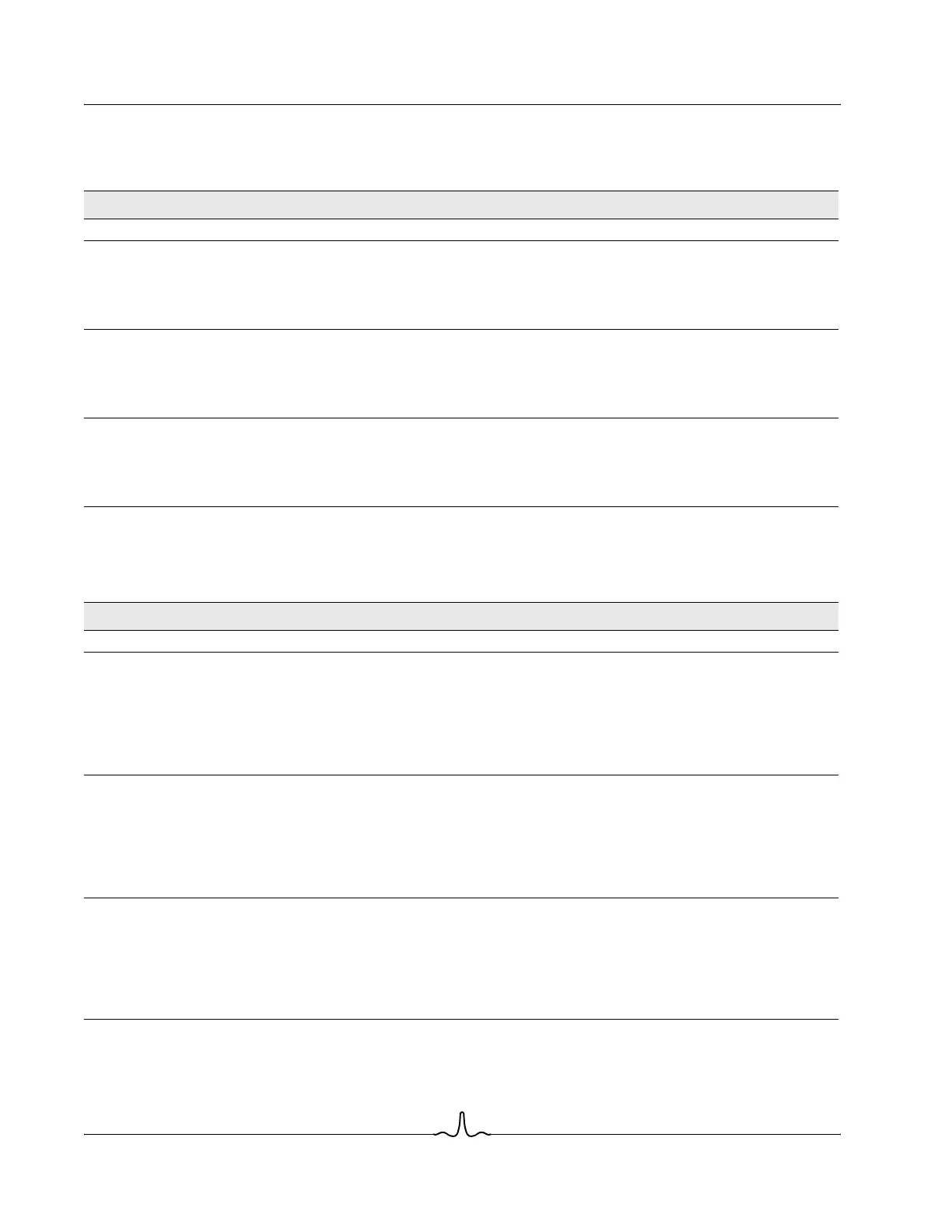

PHY TEST CONTROL REGISTER (OFFSET 0X7E2C)

Table 471: PHY Receive Error Threshold Register (Offset 0x7E28)

Bit Field Description Init Access

31:12 Reserved – 0 RO

11:8 Frame Error

Threshold

Receive frame error threshold. When the frame

error count exceeds this threshold. The frame

error attention bit is set. Threshold=2^n, where

n=bits(11:8).

0x4 (For BCM5787, BCM5787M,

BCM5754, and BCM5754M only)

0xF (For BCM5722, BCM5755,

BCM5755M, BCM5756M, BCM5757

only)

R/W

7:4 Disparity Error

Threshold

Receive 8b10b running disparity error

threshold. When the running disparity error

count exceed this threshold, the disparity error

will be set. Threshold = 2^n, where n = bits(7:4).

0x4 (For BCM5787, BCM5787M,

BCM5754, and BCM5754M only)

0xF (For BCM5722, BCM5755,

BCM5755M, BCM5756M, BCM5757

only)

R/W

3:0 Code Error

Threshold

Receive 8b10b coding error threshold. When

the code error count exceeds threshold, the

code error attention bit is set. Threshold = 2^n,

where n = bits(3:0).

0x4 (For BCM5787, BCM5787M,

BCM5754, and BCM5754M only)

0xF (For BCM5722, BCM5755,

BCM5755M, BCM5756M, BCM5757

only)

R/W

Table 472: PHY Test Control Register (Offset 0x7E2C)

Bit Field Description Init Access

31:23 Reserved – 0 RO

22 Two OS rule relaxing

(BCM5787,

BCM5787M,

BCM5754, BCM5754M

devices only)

• 1 = Relax two consecutive ordered set rule checking. The

OS count continues with alternating TS1 and TS2

• 0 = Strictly consecutive ordered set rule checking.The OS

count continues only with the same type of OS, not with

alternating TS1 and TS2

0RW

Reserved (other

devices)

0RO

20 Disable Link Down

Reset (BCM5787,

BCM5787M,

BCM5754, BCM5754M

devices only)

• 1 = To cause link down reset to LTSSM when detect link

down event.

• 0 = To not cause link down reset to LTSSM at link down

event. The link down reset will be propagated to the rest of

the chip, except the LTSSM.

0RW

Reserved (other

devices)

0RO

18 Disable Error Exit

(BCM5787,

BCM5787M,

BCM5754, BCM5754M

devices only)

• 1 = To continue receiving a frame when detect a symbol

error, until a frame delimiter is received.

• 0 = To exit receiving a frame when detect a symbol error.

0RW

Reserved (other

devices)

0RO

Loading...

Loading...