BCM5722 Programmer’s Guide

10/15/07

Broadcom Corporation

Page 509 Transceiver Registers (BCM5906/BCM5906M) Document 5722-PG101-R

SHADOW REGISTER DETAILED DESCRIPTION

The following tables describe the shadow registers bits and their function. Shadow register access is enabled by writing a 1

to bit 7 of MII register 31 (1Fh). When non-shadow register access is required, write a 0 to bit 7 of MII register 31 (1Fh).

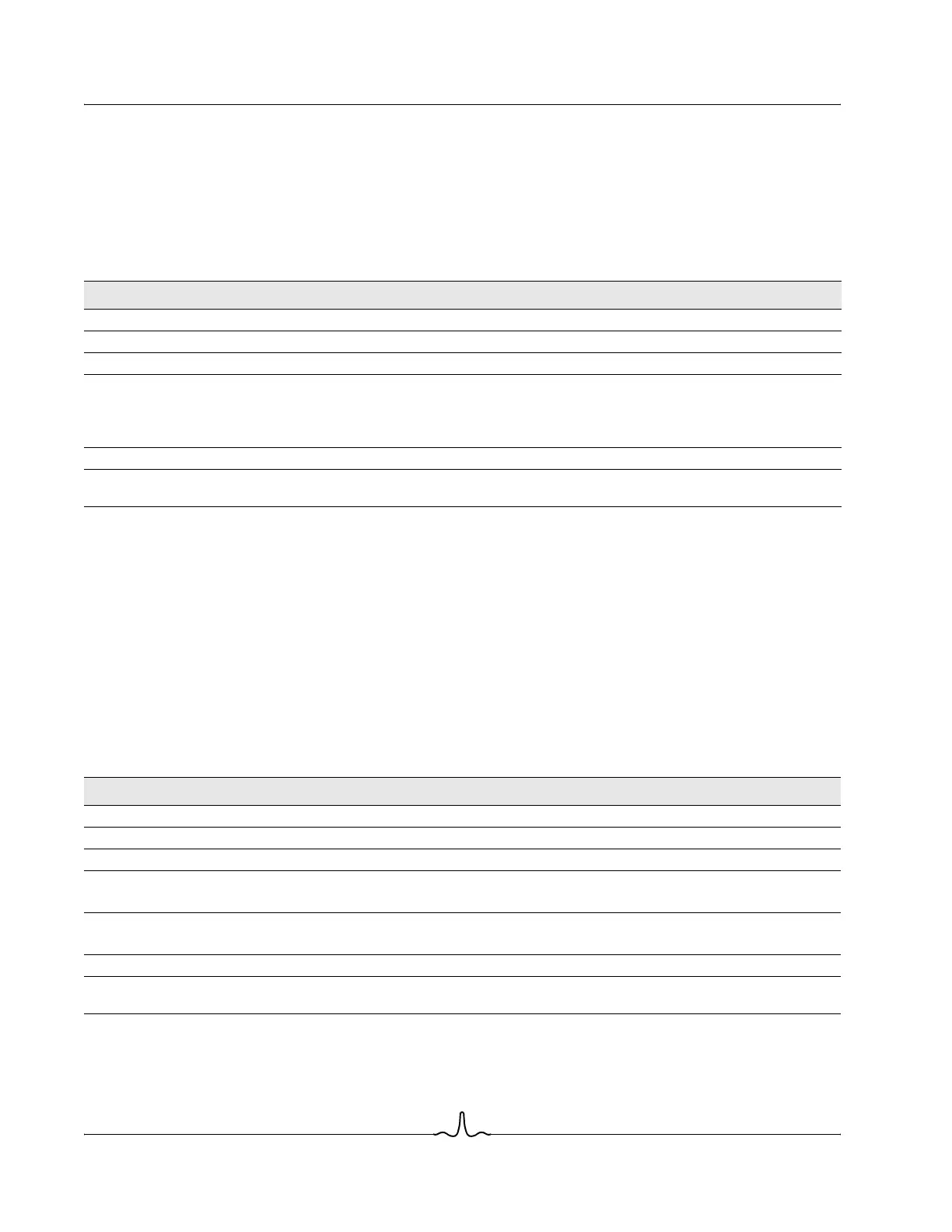

Miscellaneous Control Register (Shadow Register)

Forced Auto-MDIX Enable

When this bit is set to 0, HP. Auto-MDIX is in effect while the Auto-Negotiation is enabled. If Auto-Negotiation is not enabled

(Forced 100BT or Forced 10BT full- or half-duplex) and if Auto MDIX is still needed, set this bit to 1.

Auto-Negotiation Hardware Override

The PHY uses ANEN and F100 functions from the power-on reset values. When this bit is set to 1, the PHY uses ANEN,

F100, and FDX from MII register 0h, bits 12, 13, and 8 respectively.

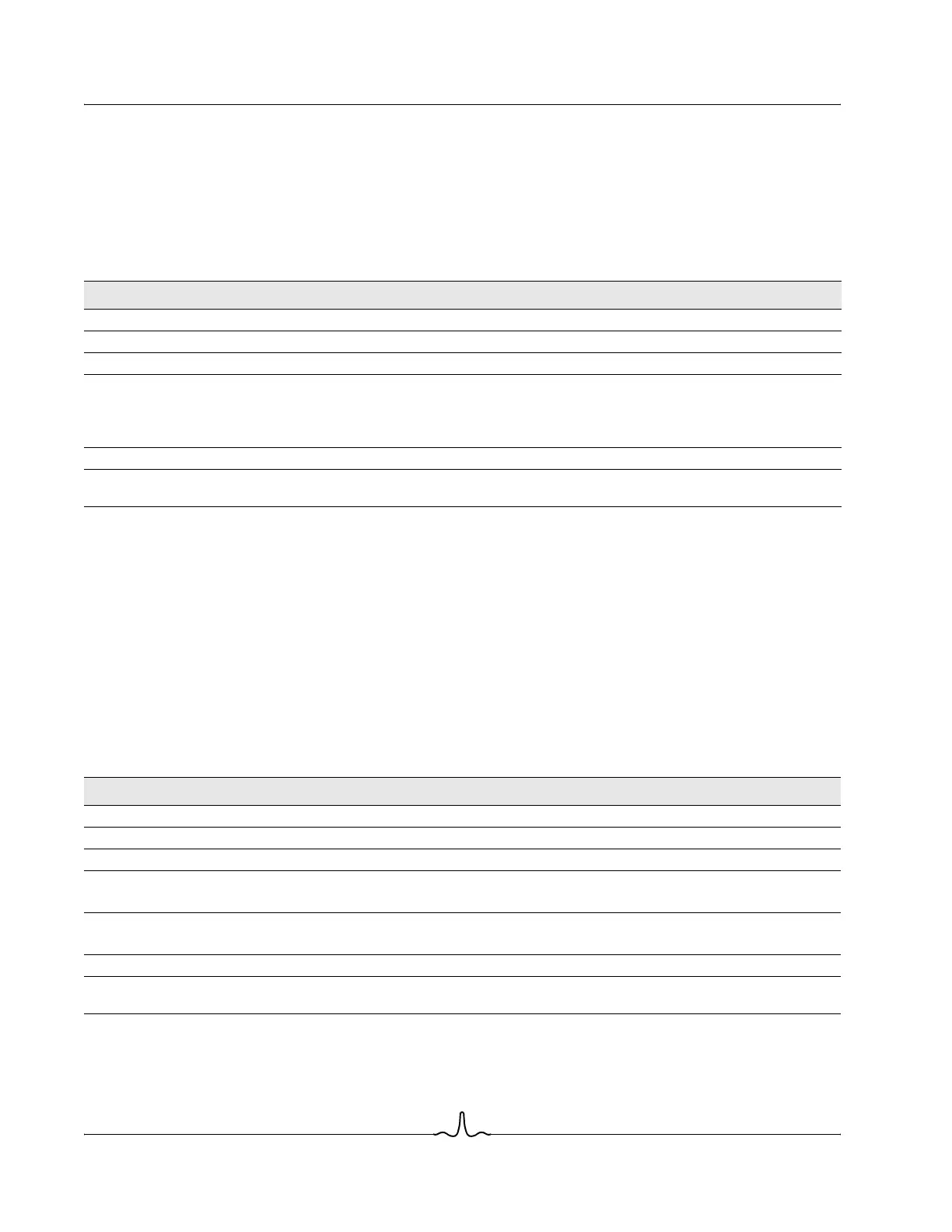

Auxiliary Status 2 Register (Shadow Register)

Table 559: Miscellaneous Control Register (Shadow Register 16d, 10h)

BIt Name R/W Description Default

15 Reserved - - 0

14 Forced Auto-MDIX Enable R/W 1 = Enable Auto-MDIX 0

13 Reserved - - 0

12 Auto-Negotiation H/W Override

Enable

R/W 0 = Use ANEN and F100 as determined by hardware

power-on reset.

1 = Ignore hardware settings for ANEN and F100. Use MII

register 0 values.

0

11:0 Reserved - - 0000h

R/W = Read/Write, RO = Read only, SC = Self Clear, LL = Latched Low, LH = Latched High, LL and LH Clear after read

operation. Use default values of reserved bit(s) when writing to reserved bit(s).

Table 560: Auxiliary Status 2 Register (Shadow Register 27d, 1Bh)

BIt Name R/W Description Default

15 MLT3 Detected R/O 1 = MLT3 detected 0h

14:12 Cable Length 100X[2:0] R/O The PHY shows the cable length in 20-meter increments

11:6 Reserved - - 00h

5 APD Enable R/W 0 = Normal mode

1 = Enable auto power-down mode

0

4 APD Sleep Timer R/W 0 = 2.5-second sleep before wake up

1 = 5.0-second sleep before wake up

0

3:0 APD Wake-Up Timer[3:0] R/W Duration of wake up 0001

R/W = Read/Write, RO = Read only, SC = Self Clear, LL = Latched Low, LH = Latched High, LL and LH Clear after read

operation. Use default values of reserved bit(s) when writing to reserved bit(s).

Loading...

Loading...