BCM5722 Programmer’s Guide

10/15/07

Broadcom Corporation

Page 191 PCI Configuration Registers Document 5722-PG101-R

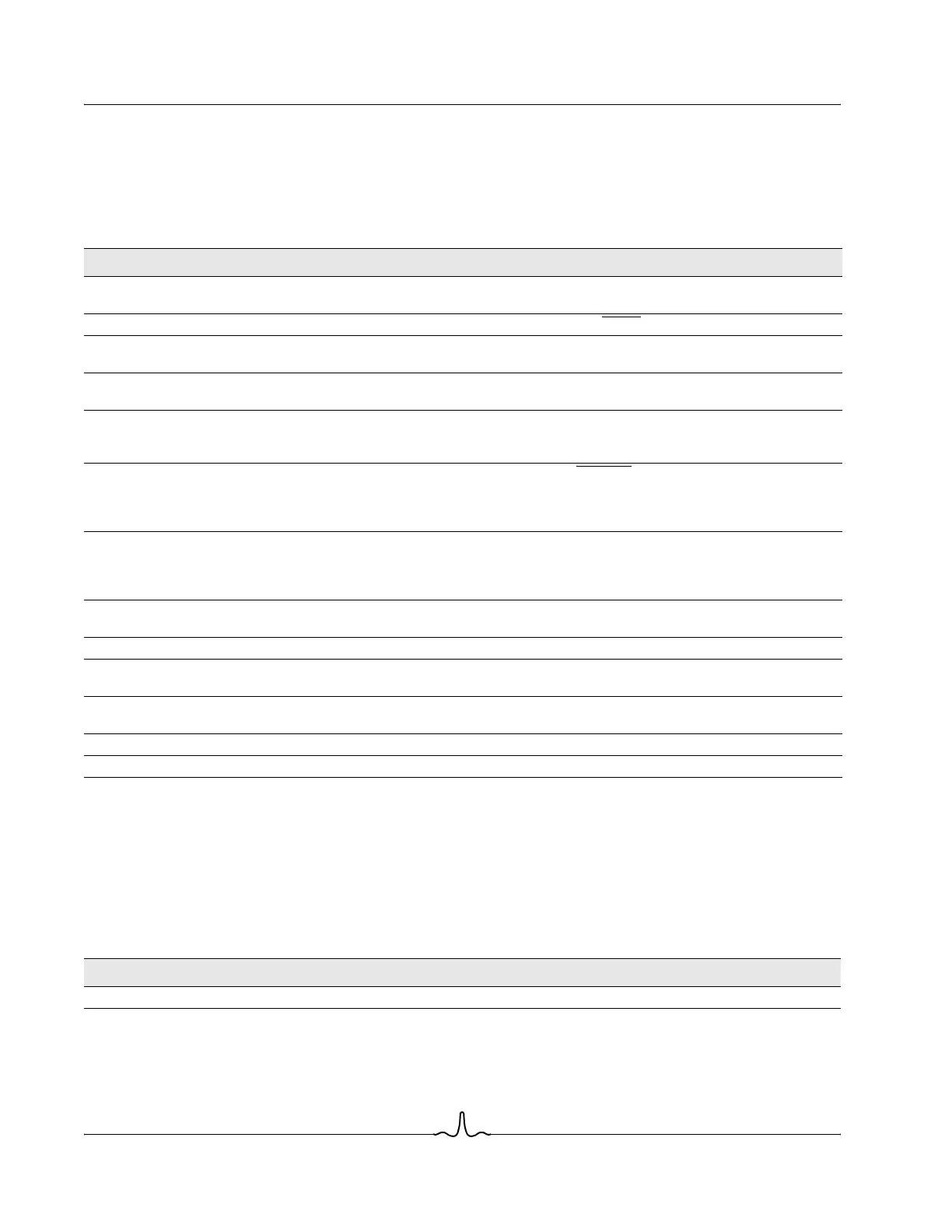

STATUS REGISTER (OFFSET 0X06)

The 16-bit Status register is used to indicate status information to the PCI-based host for PCI bus-related events. All of the

bit positions are predefined by the PCI specification. Not all bits in this register are implemented.

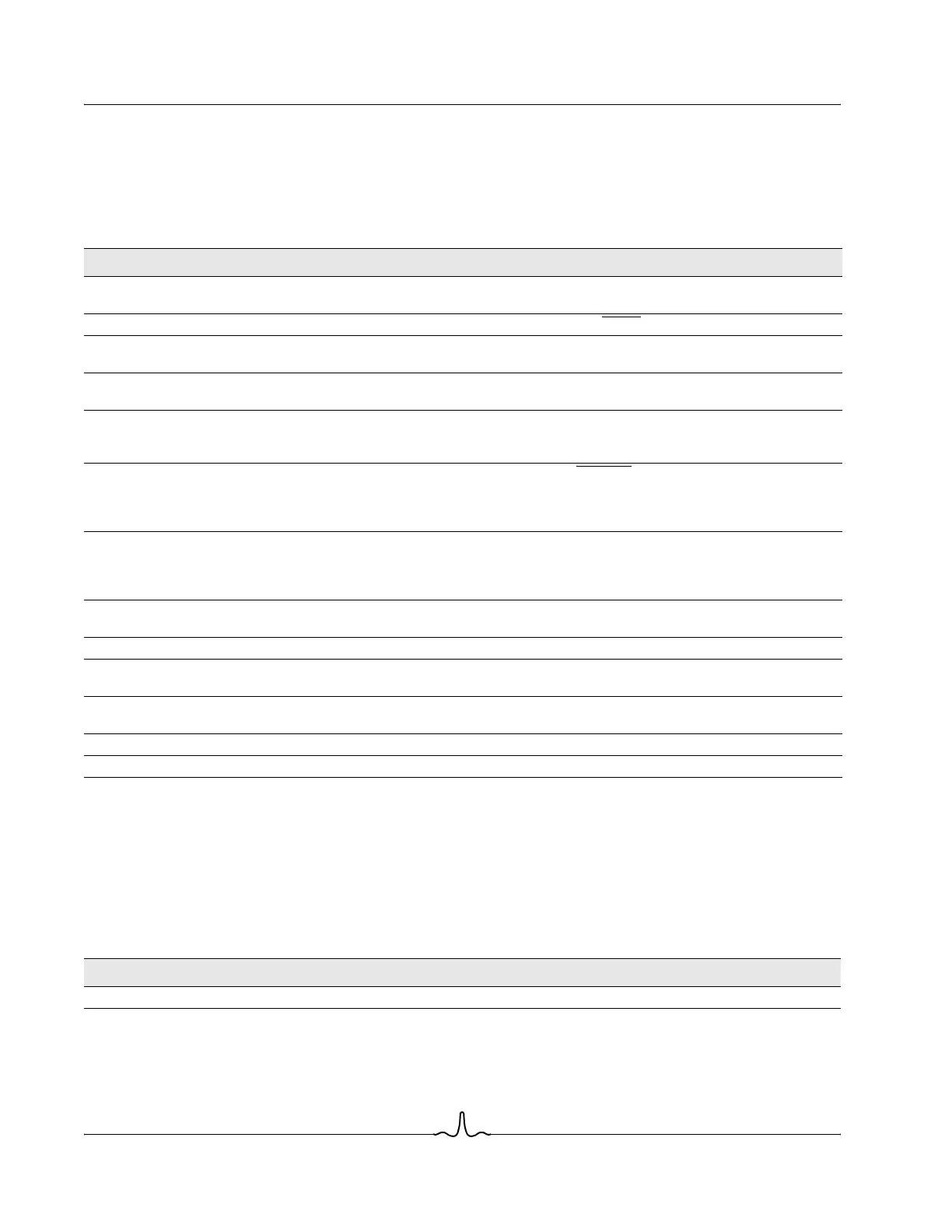

REVISION ID REGISTER (OFFSET 0X08)

The 8-bit Revision ID register is used by the manufacturer to identify the specific revision number of this adapter. Any value

is allowable. It is recommended that this field be initialized to the board revision level. This register defaults to 0x00 at power-

on reset. This register may be written by the internal RISCs but cannot be written via the host PCI interface. Normally, this

register is loaded with the appropriate Revision ID after reset by bootcode that resides in the NVRAM.

Table 96: Status Register (Offset 0x06)

Bit Field Description Init Access

15 Detected Parity Error Indicates a data parity error was detected even if parity

reporting was not enabled.

0R/W2C

14 Signaled System Error Indicates this device asserted system error (SERR

). 0 R/W2C

13 Received Master Abort Indicates this device was a bus master and the transaction

was terminated with a master-abort.

0R/W2C

12 Received Target Abort Indicates this device was a bus master and received a

target-abort.

0R/W2C

11 Signaled Target Abort Indicates this device initiated a target-abort. This bit is only

set if an external master disappears during a target

operation.

0R/W2C

10:9 DEVSEL Timing These bits encode the slowest timing of DEVSEL

, except

for configuration cycles. Valid entries are 00 for fast, 01 for

medium, and 10 for slow. The device is capable of fast

timing and these two bits are hardwired to 00.

00 RO

8 Master Data Parity Error Indicates that this device was a bus master when a parity

error was detected and reporting of parity errors is

enabled. The device is capable of operating with this bit

set.

0R/W2C

7 Fast Back-to-Back

Capable

Indicates whether fast back-to-back transactions can be

accepted when transactions are not to the same agent.

0RO

6Reserved – 0 RO

5 66 MHz Capable Indicates whether this device can operate on a 66-MHz

PCI bus.

0RO

4 Capabilities List Indicates whether this device has a capabilities list. The

device has a capabilities list, so this bit is hardwired to 1.

1RO

3 Interrupt Status Indicates this device has generated an interrupt. 0 RO

2:0 Reserved – 0 RO

Table 97: Revision ID Register (Offset 0x08)

Bit Field Description Init Access

8:0 Revision ID Revision of this part (“Revision Levels” on page 8)0h R/W

a

a. Not writable by PCI configuration access.

Loading...

Loading...