MIPS R4000 Microprocessor User's Manual 91

Memory Management

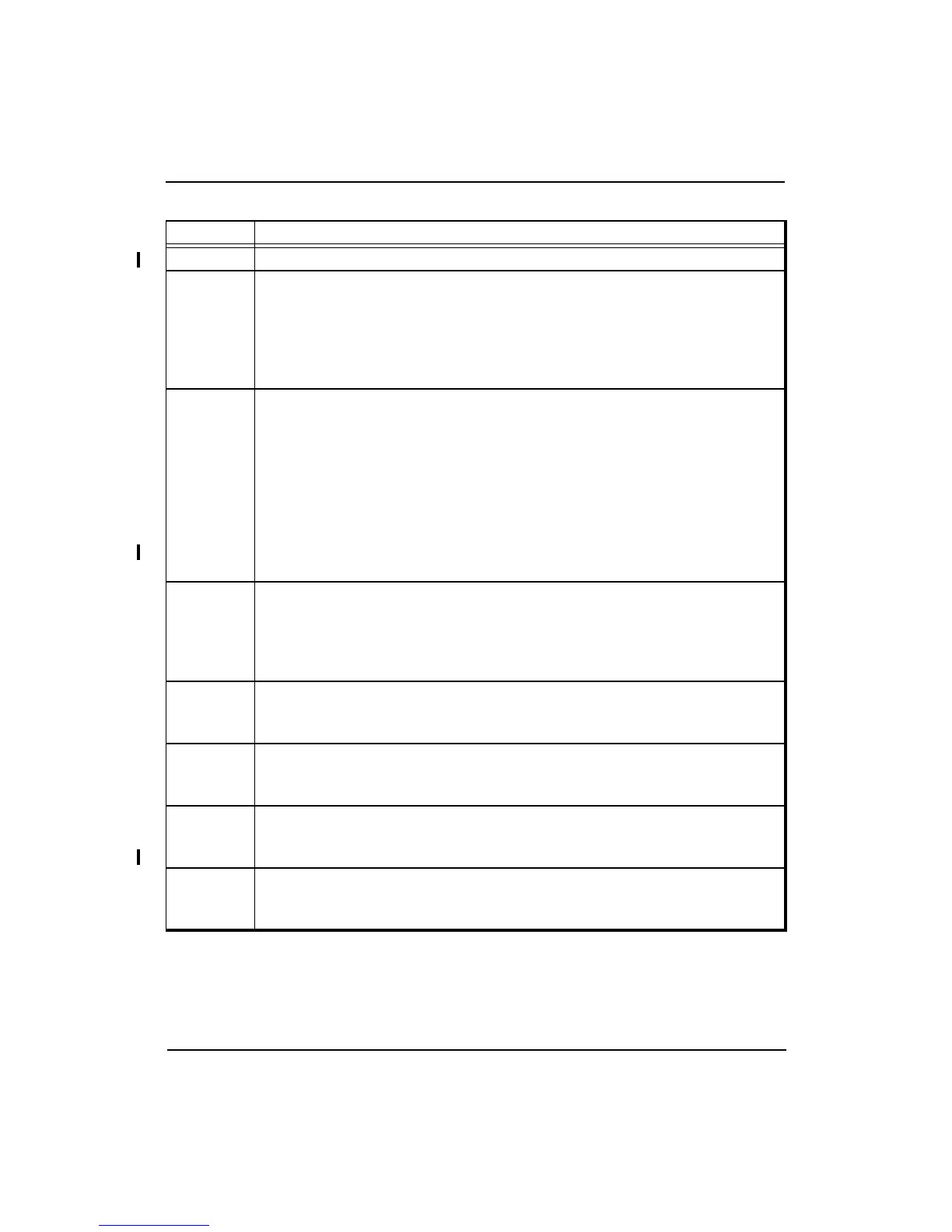

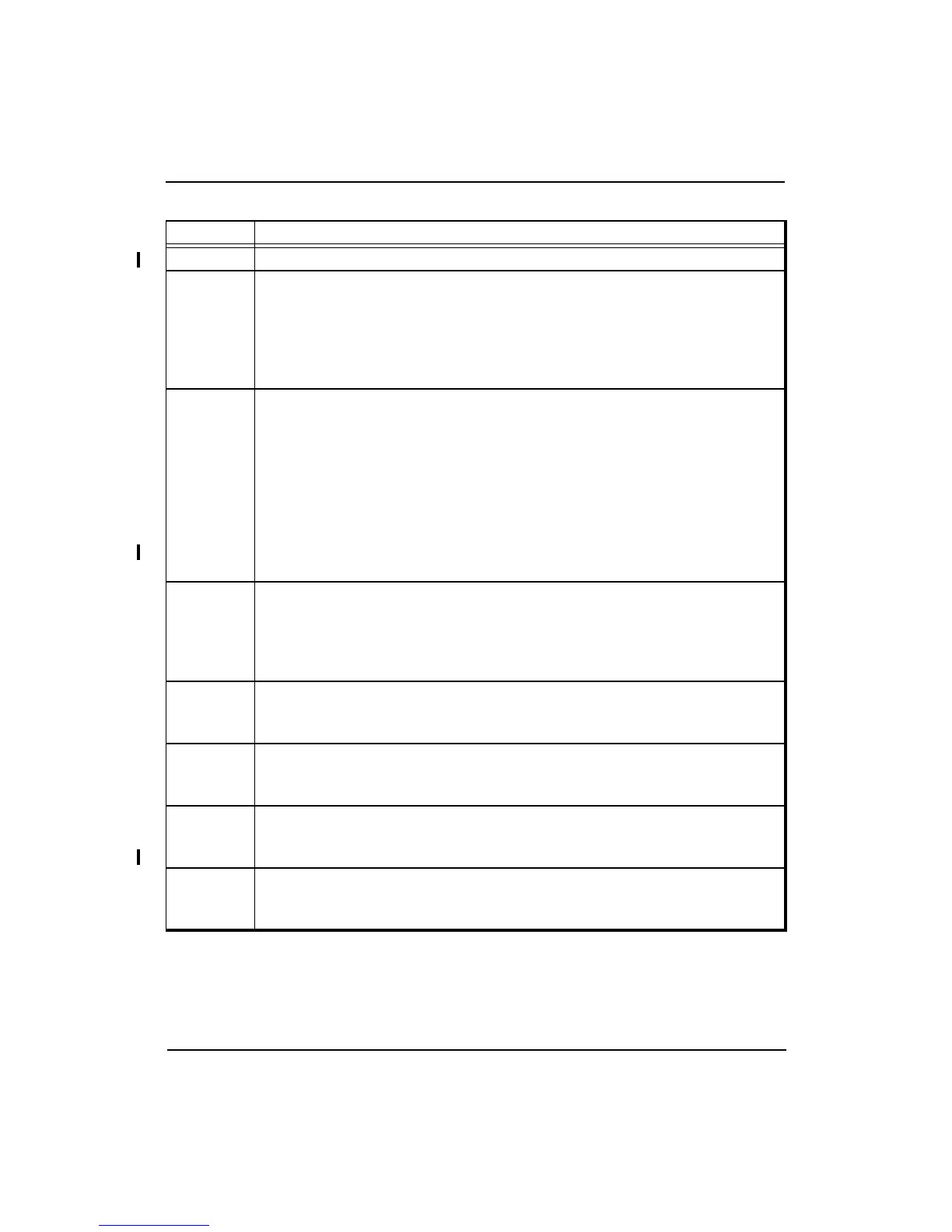

Table 4-12 Config Register Fields

Field Description

CM Master-Checker Mode (1 → Master/Checker Mode is enabled).

EC

System clock ratio:

0 → processor clock frequency divided by 2

1 → processor clock frequency divided by 3

2 → processor clock frequency divided by 4

3 → processor clock frequency divided by 6 (R4400 processor only)

4 → processor clock frequency divided by 8 (R4400 processor only)

EP

Transmit data pattern (pattern for write-back data):

0 → D Doubleword every cycle

1 → DDx 2 Doublewords every 3 cycles

2 → DDxx 2 Doublewords every 4 cycles

3 → DxDx 2 Doublewords every 4 cycles

4 → DDxxx 2 Doublewords every 5 cycles

5 → DDxxxx 2 Doublewords every 6 cycles

6 → DxxDxx 2 Doublewords every 6 cycles

7 → DDxxxxxx 2 Doublewords every 8 cycles

8 → DxxxDxxx 2 Doublewords every 8 cycles

SB

Secondary Cache line size:

0 → 4 words

1 → 8 words

2 → 16 words

3 → 32 words

SS

Split Secondary Cache Mode

0 → instruction and data mixed in secondary cache (joint cache)

1 → instruction and data separated by SCAddr(17)

SW

Secondary Cache port width

0 → 128-bit data path to S-cache

1 → Reserved

EW

System Port width

0 → 64-bit

1, 2, 3 → Reserved

SC

Secondary Cache present

0 → S-cache present

1 → no S-cache present

Loading...

Loading...