Chapter 4

92 MIPS R4000 Microprocessor User's Manual

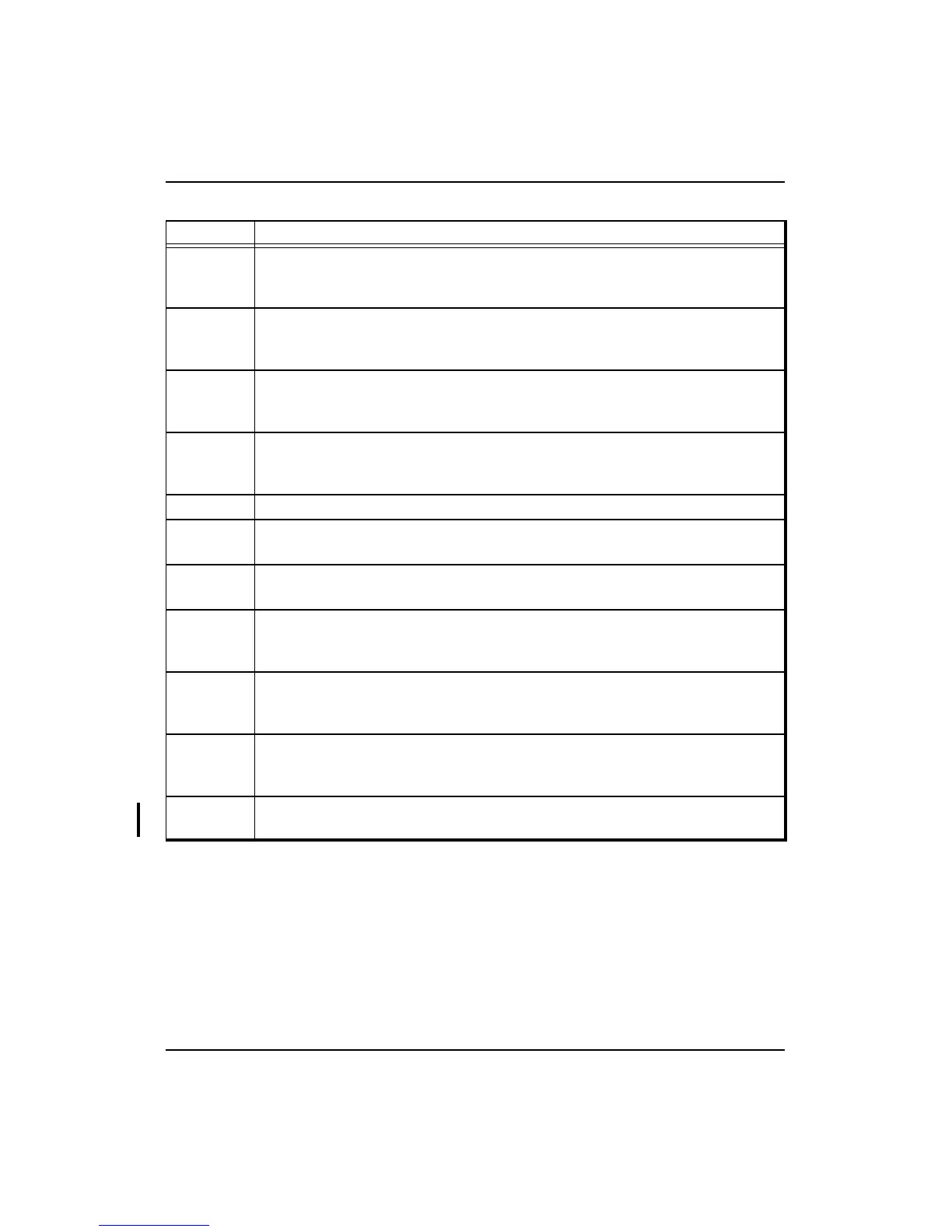

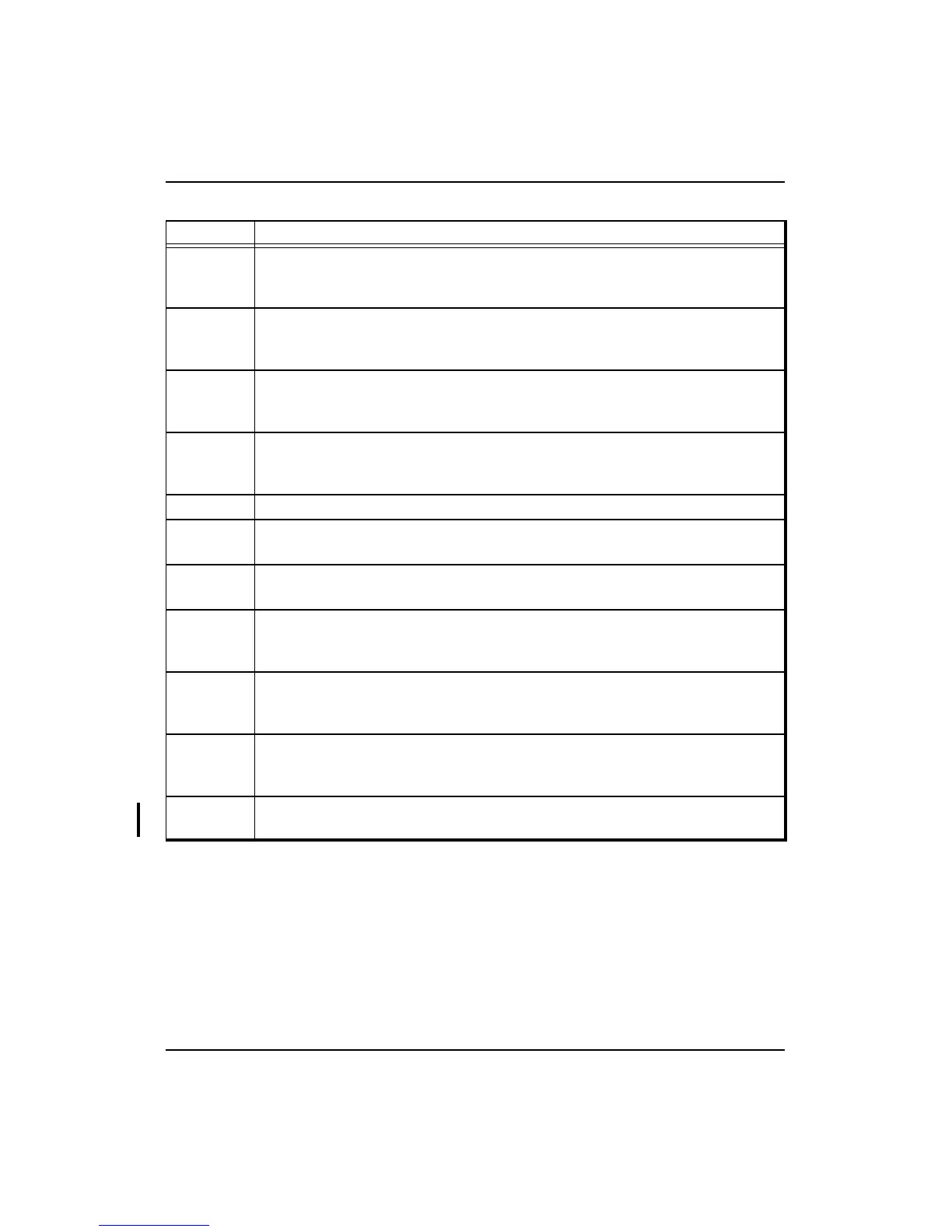

Table 4-12 (cont.) Config Register Fields

Field Name Description

SM

Dirty Shared coherency state

0 → Dirty Shared coherency state is enabled

1 → Dirty Shared state is disabled

BE

BigEndianMem

0 → kernel and memory are little endian

1 → kernel and memory are big endian

EM

ECC mode enable

0 → ECC mode enabled

1 → parity mode enabled

EB

Block ordering

0 → sequential

1 → sub-block

0 Reserved. Must be written as zeroes, returns zeroes when read.

IC

Primary I-cache Size (I-cache size = 2

12+IC

bytes). In the R4000 processor,

this is set to 8 Kbytes; in the R4400 processor, this is set to 16 Kbytes.

DC

Primary D-cache Size (D-cache size = 2

12+DC

bytes). In the R4000 processor,

this is set to 8 Kbytes, in the R4400 processor, this is set to 16 Kbytes.

IB

Primary I-cache line size

0 → 16 bytes

1 → 32 bytes

DB

Primary D-cache line size

0 → 16 bytes

1 → 32 bytes

CU

Update on Store Conditional

0 → Store Conditional uses coherency algorithm specified by TLB

1 → SC uses cacheable coherent update on write

K0

kseg0 coherency algorithm (see EntryLo0 and EntryLo1 registers and the C

field of Table 4-6)

Loading...

Loading...