MIPS R4000 Microprocessor User's Manual 145

CPU Exception Processing

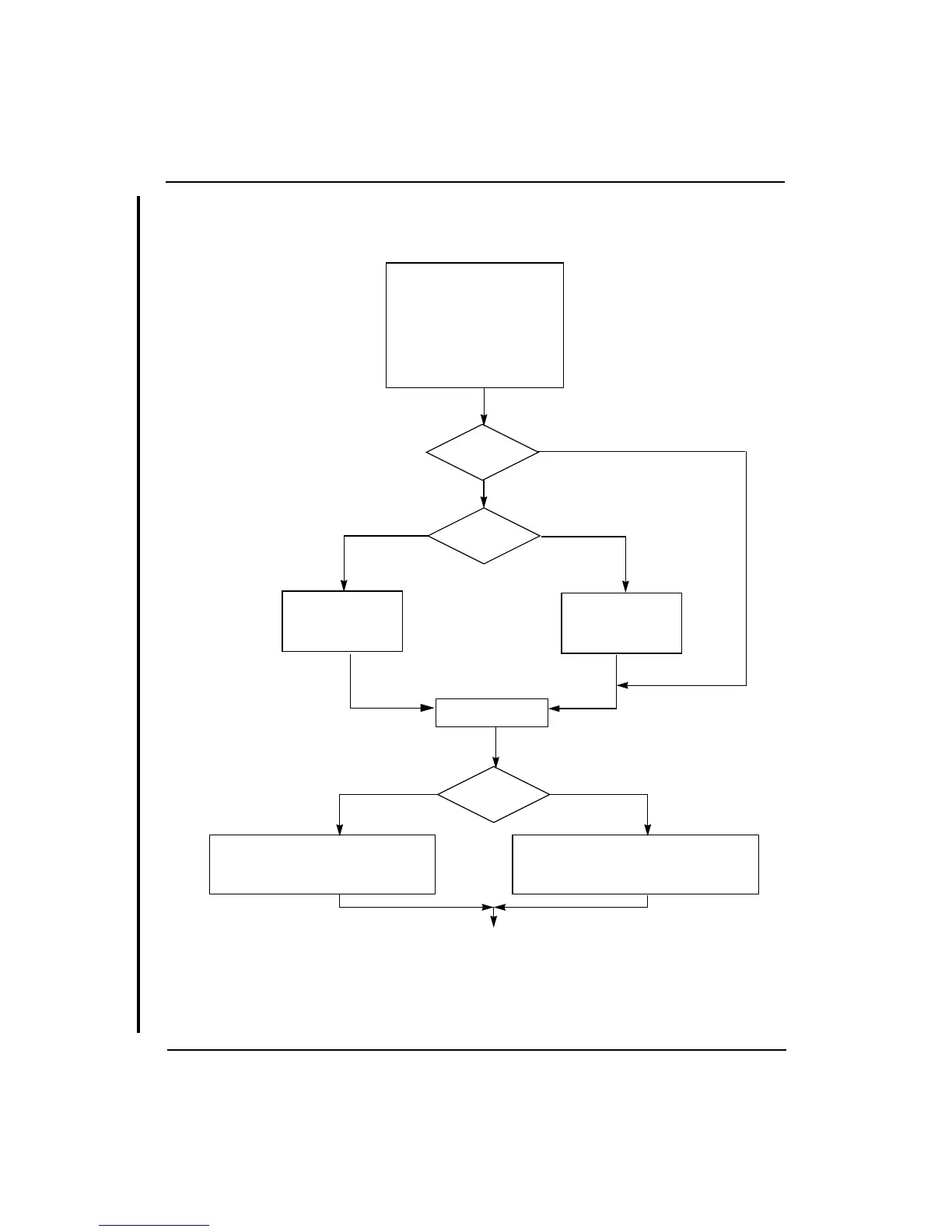

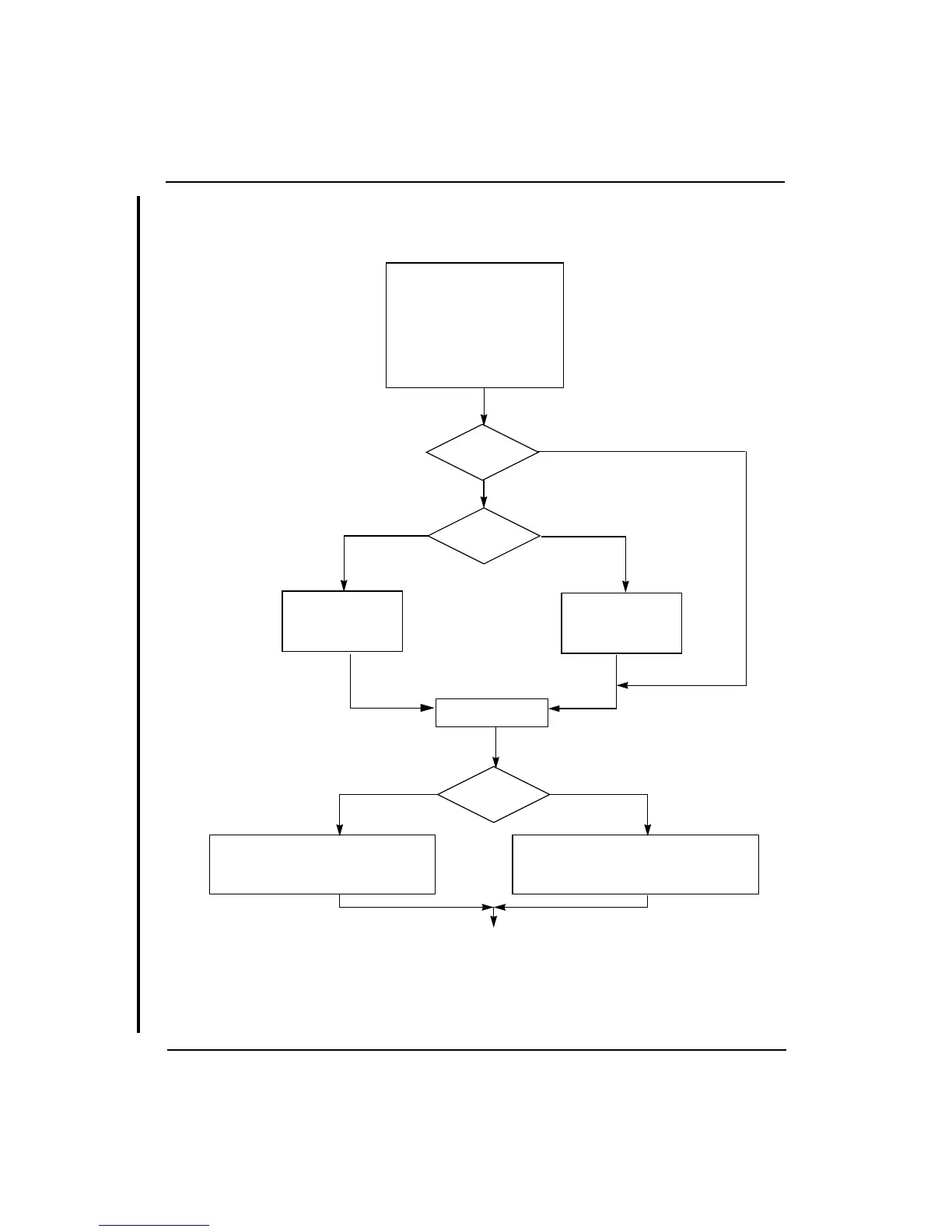

Figure 5-18 General Exception Handler (HW)

PC <- 0xFFFF FFFF BFC0 0200 + 180

PC <- 0xFFFF FFFF 8000 0000 + 180

EXL <- 1

BEV

=1 (bootstrap)=0

To General Exception Servicing Guidelines

(unmapped, cached)

(unmapped, uncached)

Exceptions other than Reset, Soft Reset, NMI, CacheError or first-level miss

Note: Interrupts can be masked by IE or IMs

and Watch is masked if EXL = 1

Check if exception within

Processor forced to Kernel Mode

(normal)

EPC <- PC

Instr. in

Yes

No

EPC <- (PC - 4)

Br.Dly. Slot?

EXL

(SR1)

=1

=0

BadVA is set only for

TLB- Invalid, Modified,

Note: not set if it is a Bus Error

Cause 31 (BD) <- 1

Cause 31 (BD) <- 0

Refill- and VCED/I exceptions

EnHi, X/Context are set only for

*TLB- Invalid, Modified,

& Refill exceptions

Set Cause Register

EnHi <- VPN2, ASID

Context <- VPN2

EXCCode, CE

Set Watch Register

Set FP Control Status Register

*Watch & FP Control Status Register

are only set if the respective exception

occurs.

& interrupt disabled

Comments

another exception

Set BadVA

Loading...

Loading...