Chapter 5

146 MIPS R4000 Microprocessor User's Manual

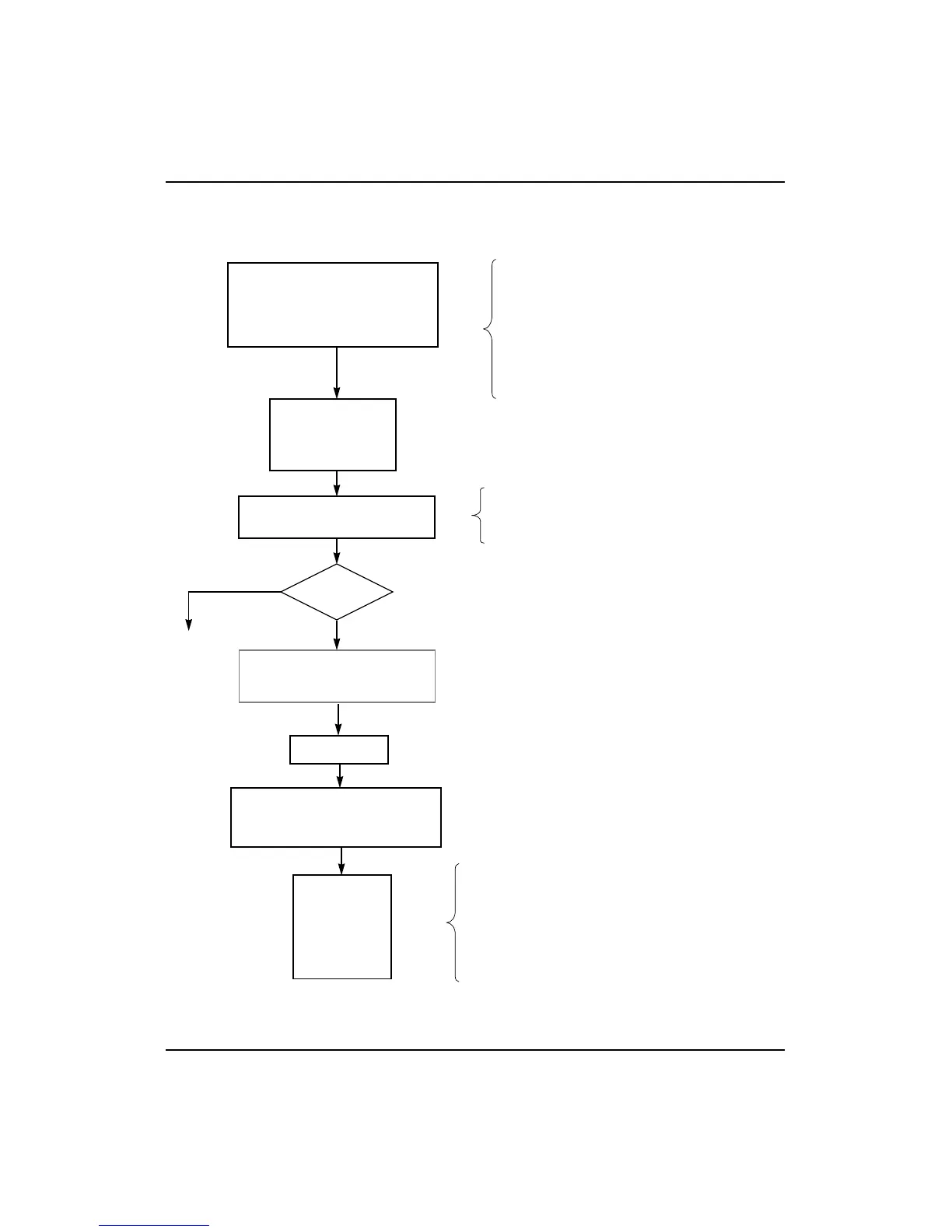

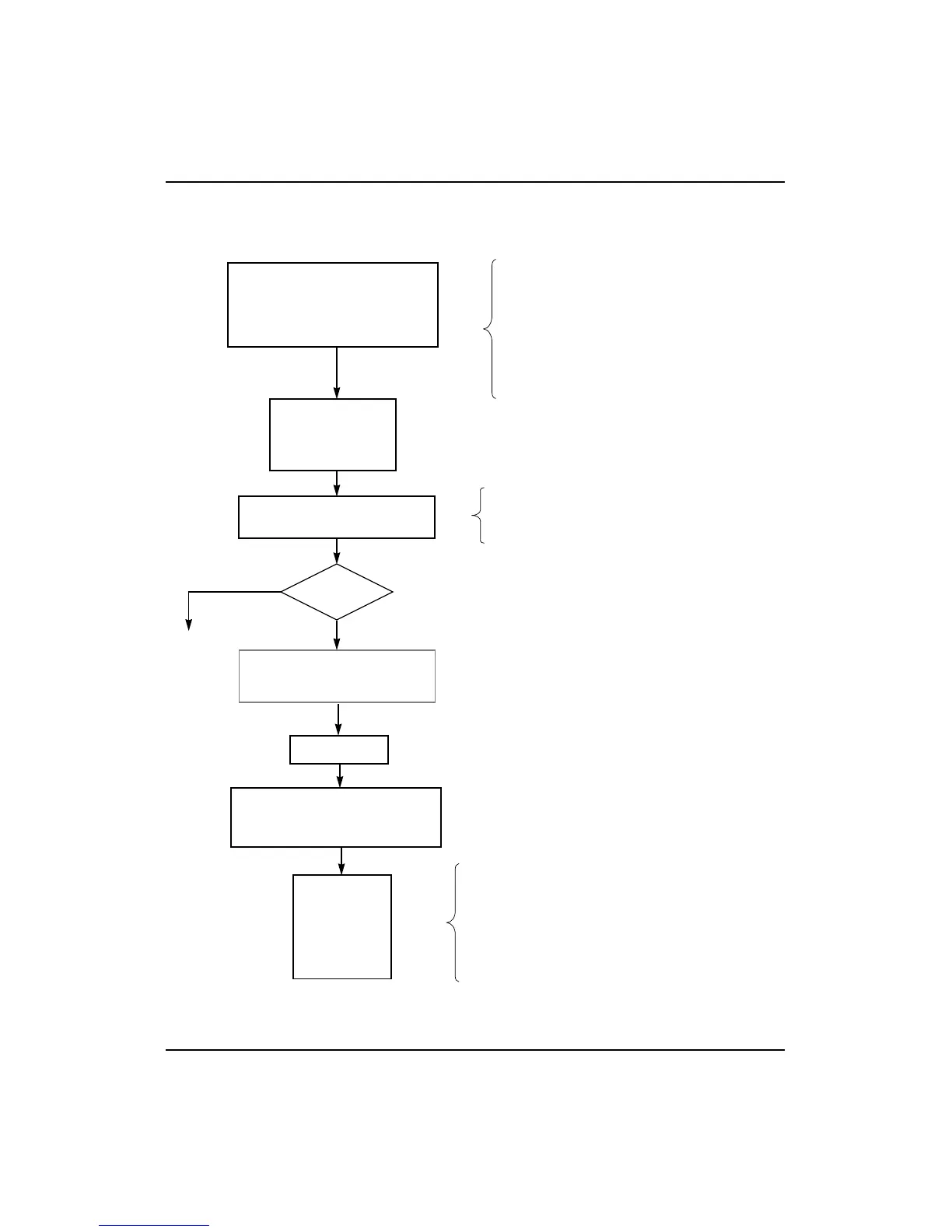

Figure 5-19 General Exception Servicing Guidelines (SW)

MFC0 -

X/Context

EPC

Status

Cause

EXL <- 0

Check CAUSE REG. & Jump to

appropriate Service Code

EXL = 1

MTC0 -

EPC

STATUS

ERET

* Unmapped vector so TLBMod, TLBInv,

TLB Refill exceptions not possible

* EXL=1 so Watch, Interrupt exceptions disabled

*Only CacheError, Reset, Soft Reset, NMI

* OS/System to avoid all other exceptions

* After EXL=0, all exceptions allowed.

(except interrupt if masked by IE or IM

and CacheError if masked by DE)

Comments

exceptions possible.

KSU<- 00

(optional - only to enable Interrupts while keeping Kernel Mode)

MTC0 -

(Set Status Bits:)

& IE=1

Reset the processor

Status

* PC <- EPC; EXL <- 0

* LLbit <- 0

* ERET is not allowed in the branch delay slot of

* Processor does not execute the instruction which is

in the ERET’s branch delay slot

another Jump Instruction

Optional: Check only if 2nd-level TLB miss

=1

=0

Service Code

bit 21(TS)

Loading...

Loading...