MIPS R4000 Microprocessor User's Manual 149

CPU Exception Processing

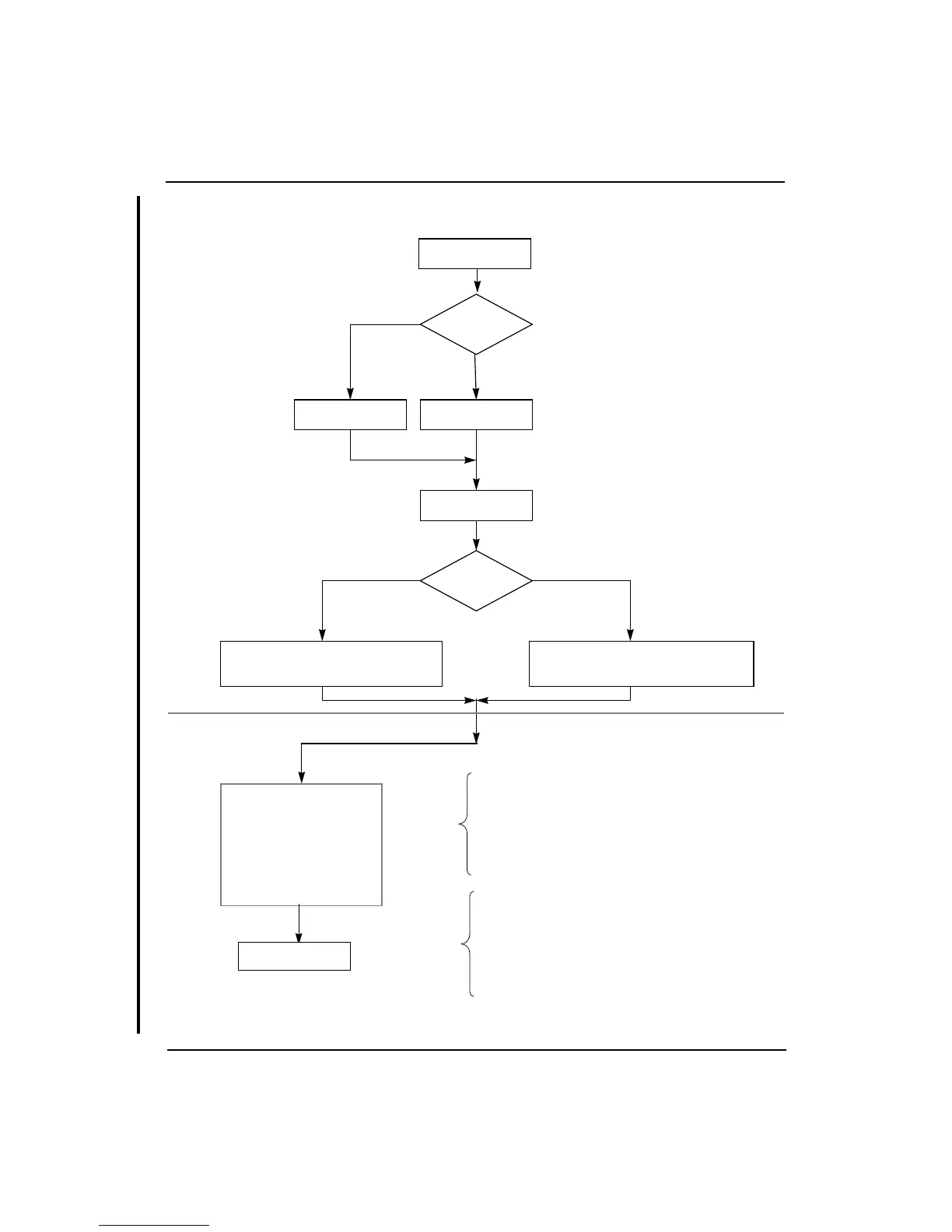

Figure 5-22 Cache Error Exception Handling (HW) and Servicing Guidelines (SW)

Set CacheErr Reg.

Cache Error Exception Handling (HW)

ERL <- 1

PC <- 0xFFFF FFFF BFC0 0200 + 100

BEV

PC <- 0xFFFF FFFF A000 0000 + 100

=1

=0

(unmapped, uncached)

(unmapped, uncached)

Note: Can be masked/disabled by DE (SR16) bit = 1

(bootstrap)

(normal)

ErrEPC <- PC

Instr. in

Yes

No

ErrEPC <- (PC - 4)

Br. Dly. Slot?

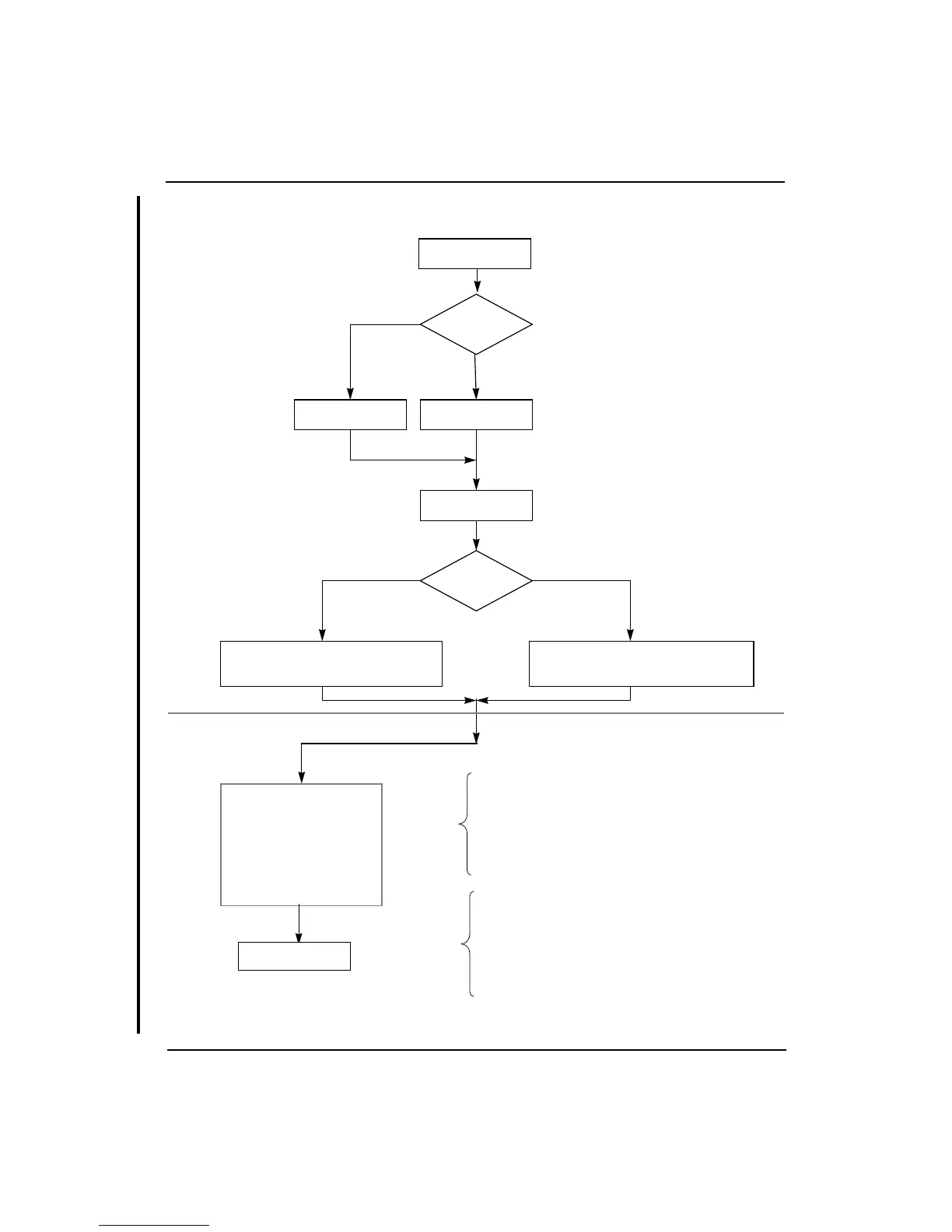

Servicing Guidelines (SW)

Service Code

ERET

* ERET is not allowed in the branch delay slot of

* Unmapped Uncached vector so

TLB related & Cache Error Exception not possible

* ERL=1 so Interrupt exceptions disabled

*Only Reset, Soft Reset, NMI

* OS/System to avoid all other exceptions

* Processor does not execute the instruction which is

* PC <- ErrorEPC; ERL <- 0

* LLbit <- 0

Comments

exceptions possible.

in the ERET’s branch delay slot

another Jump Instruction

Loading...

Loading...