Chapter 5

148 MIPS R4000 Microprocessor User's Manual

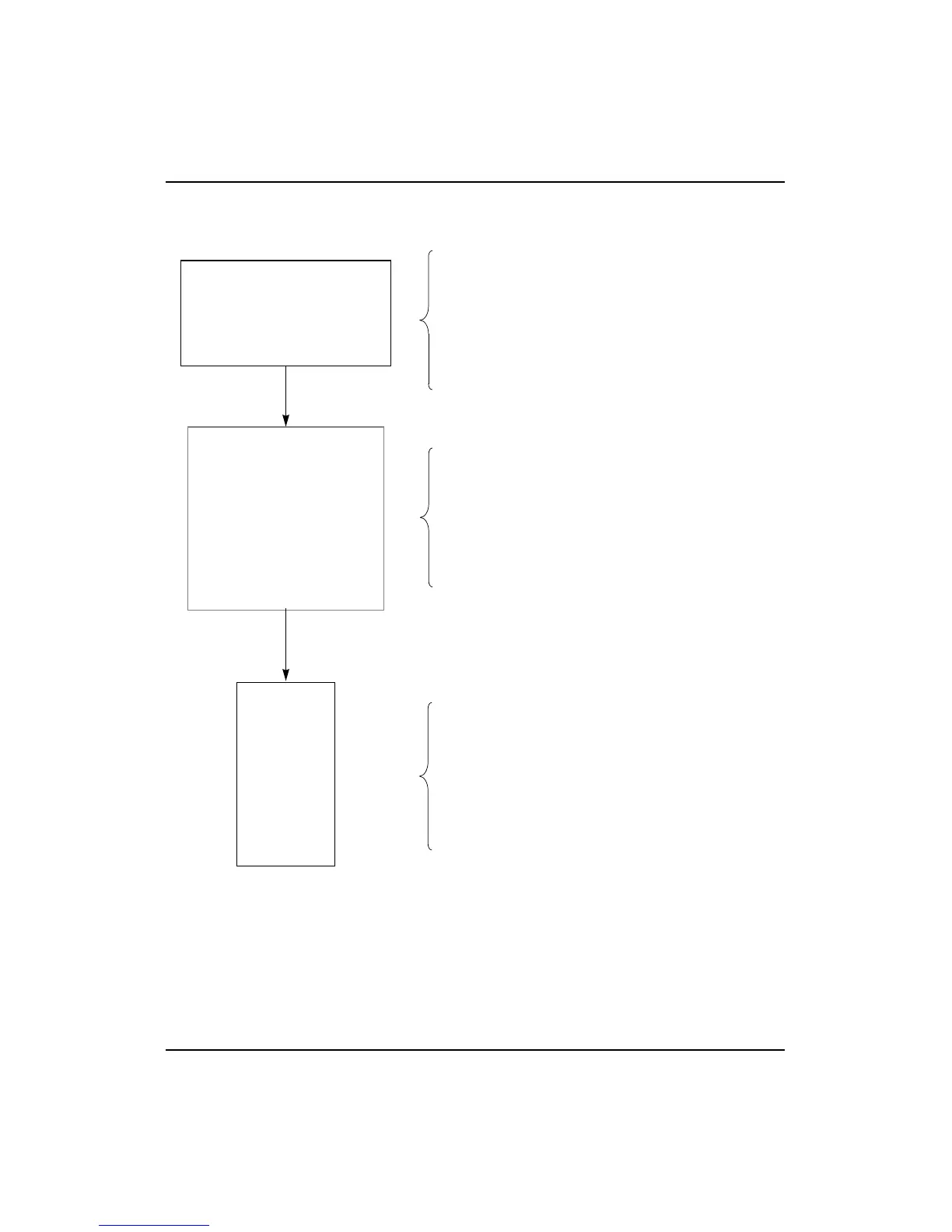

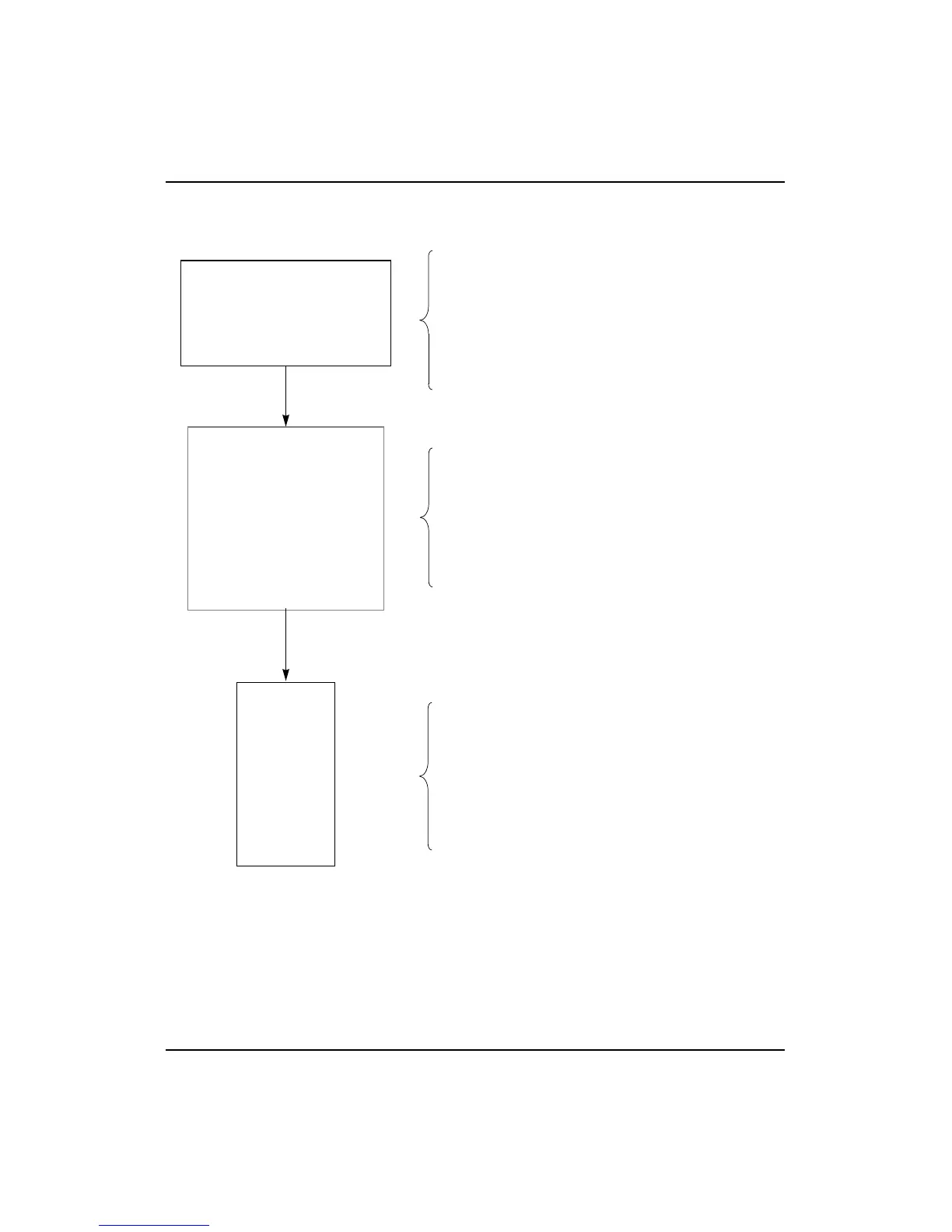

Figure 5-21 TLB/XTLB Exception Servicing Guidelines (SW)

MFC0 -

CONTEXT

Service Code

ERET

* Unmapped vector so TLBMod, TLBInv,

TLB Refill or VCEP exceptions

* EXL=1 so Watch, Interrupt exceptions disabled

*Only CacheError, Reset, Soft Reset, NMI

* OS/System to avoid all other exceptions

* PC <- EPC; EXL <- 0

* LLbit <- 0

Comments

exceptions possible.

* There could be a TLB miss again during the mapping

not possible

of the data or instruction address. The processor will

jump to the general exception vector since the EXL is 1.

(Option to complete the first level refill in the general

* Load the mapping of the virtual address in Context Reg.

Move it to ENLO and Write into the TLB

* ERET is not allowed in the branch delay slot of

* Processor does not execute the instruction which is

in the ERET’s branch delay slot

another Jump Instruction

exception handler or ERET to the original instruction

and take the exception again)

Loading...

Loading...