MIPS R4000 Microprocessor User's Manual 177

Floating-Point Unit

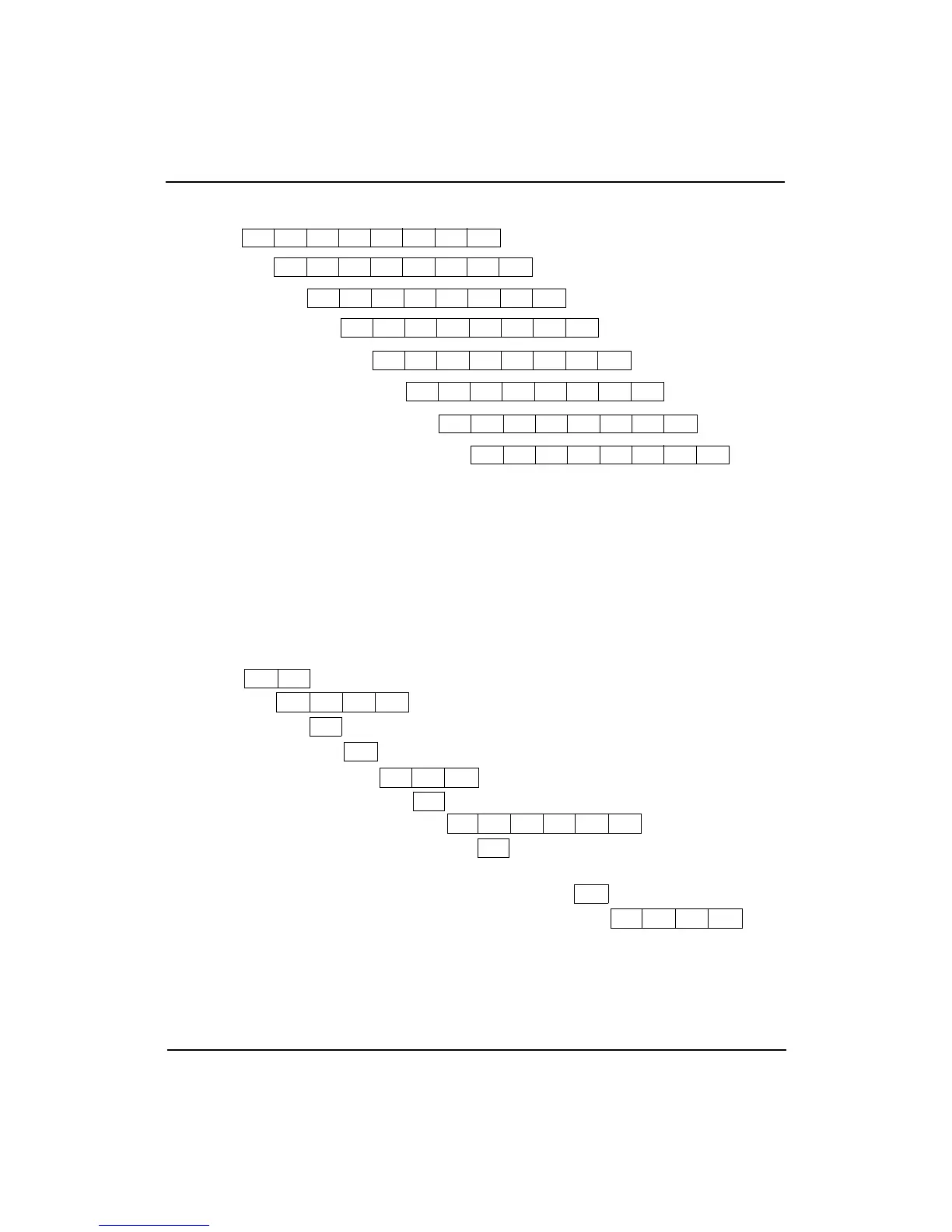

Figure 6-12 MUL.D Instruction Scheduling in the FPU Multiplier

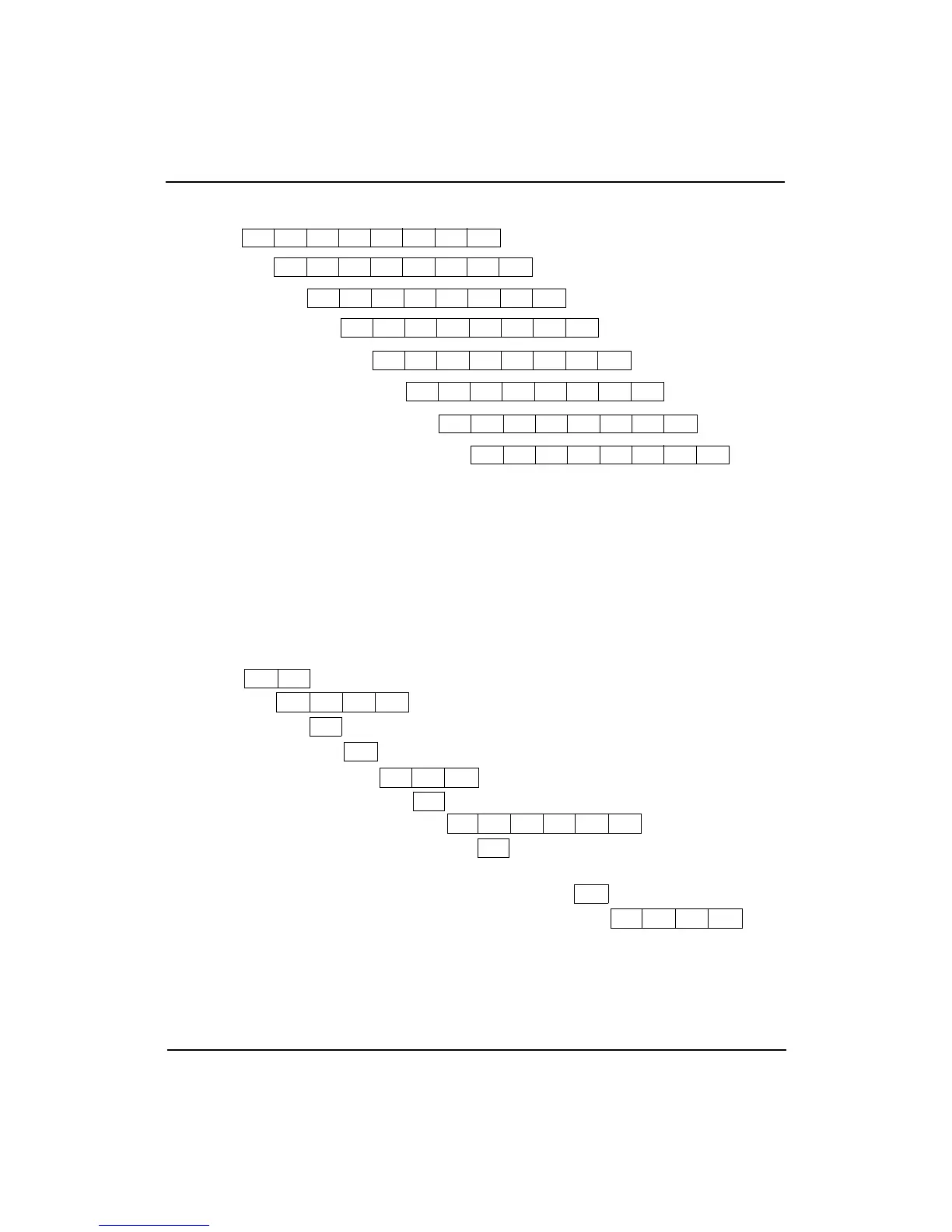

FPU Adder Constraints

Following are the constraints that must be met in the FPU adder op unit.

Cycle Overlap. The adder op unit must allow a clock cycle overlap

between each newly issued instruction and the instruction being

completed, as shown in Figure 6-13.

Figure 6-13 Instruction Cycle Overlap in FPU Adder

UMMMMN N/A R

U MMMMN N/A R

UMMMMN N/A R

UMMMMN N/A R

UMMMMN N/A R

UMMMMN N/A R

MUL.D

MUL.[S.D]

MUL.[S.D]

MUL.[S.D]

MUL.[S.D]

MUL.[S.D]

MUL.[S.D]

No

No

No

Yes

Yes

Yes

UMMMMN N/A R

Yes

UMMMMN N/A R

MUL.[S.D]

I1

I2

I3

I4

I5

I6

I7

I8

Legal to Issue?

– – – – – – – – – – – – – – – – –

– – – – – – – – – – – – – –

– – – – – –

– – – – – – – – –

– – – – – – – – – – –

– – –

U S+A A+R R+S

NEG.[S,D]

ADD.[S,D]

NOP

NOP

C.COND.[S,D]

NOP

SQRT.[S,D]

US

U

U

UAR

U

U E A+R

. . .

A+R R

NOP

U

. . .

NOP

U

USAR

ADD.[S,D]

. . .

Loading...

Loading...