MIPS R4000 Microprocessor User's Manual 223

Initialization Interface

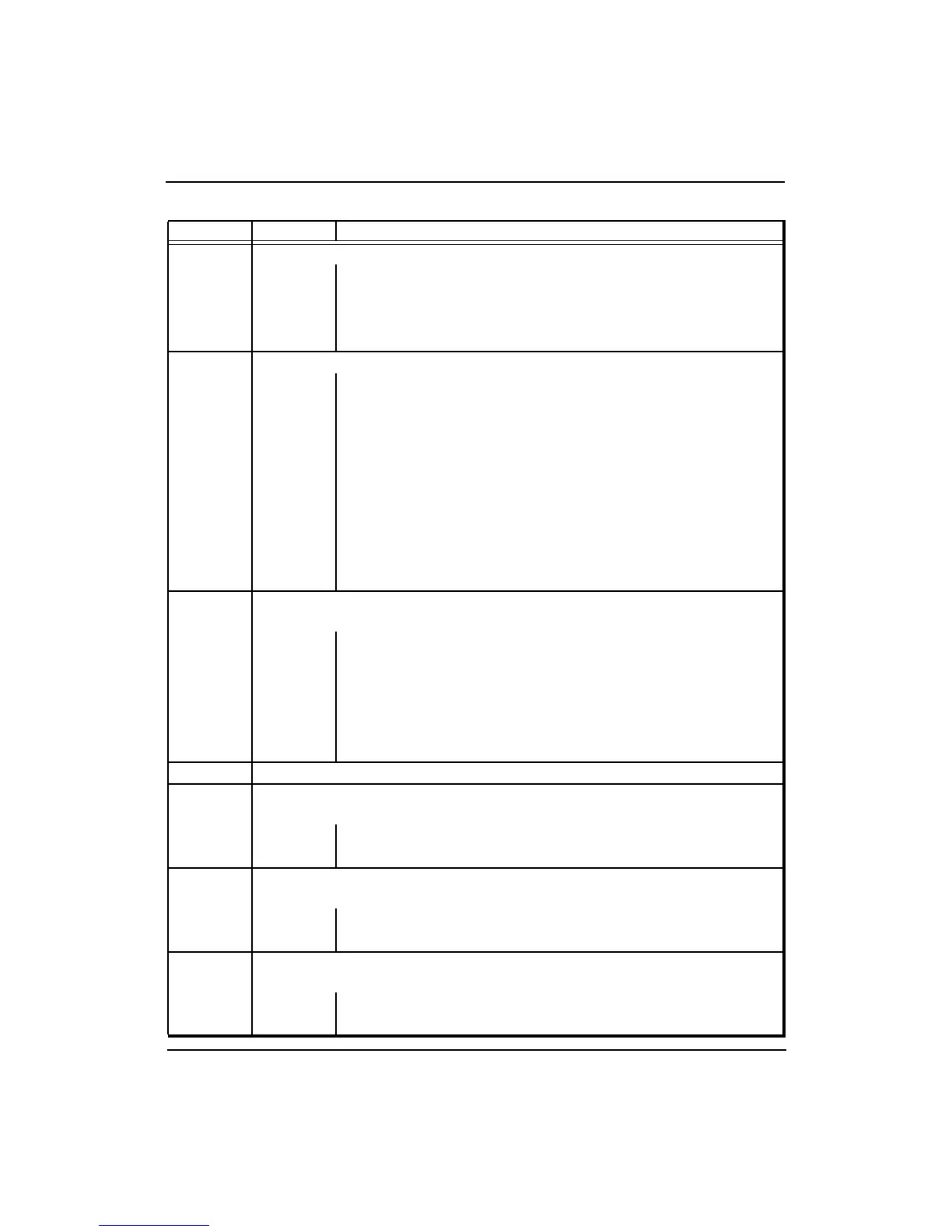

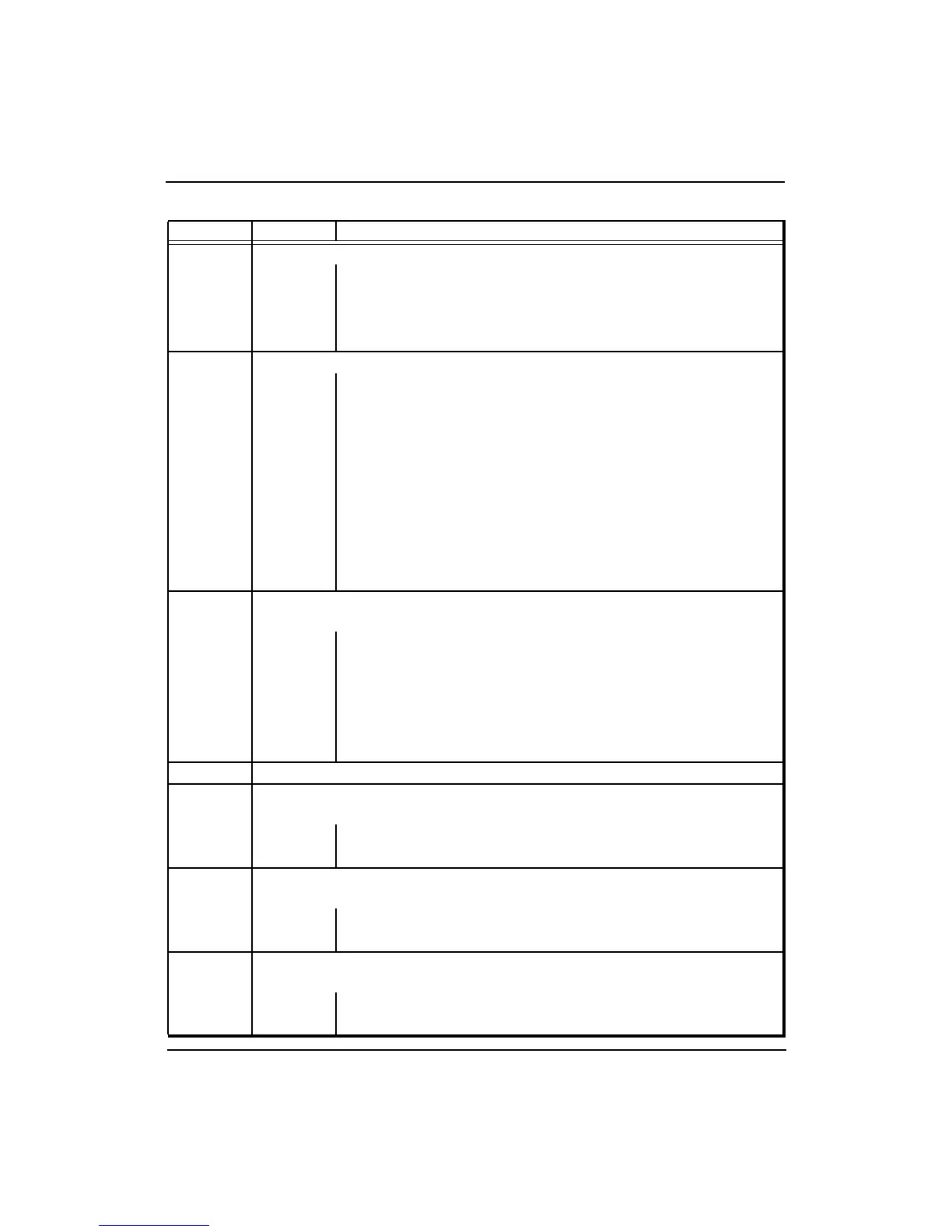

Table 9-1 (cont.) Boot-Mode Settings

Serial Bit Value Mode Setting

9:10

SCBlkSz: Secondary cache line length, bit 10 most significant

0 4 words

1 8 words

2 16 words

3 32 words

11:14

XmitDatPat: System interface data rate, bit 14 most significant

0D

1 DDx

2 DDxx

3 DxDx

4 DDxxx

5 DDxxxx

6 DxxDxx

7 DDxxxxxx

8 DxxxDxxx

9-15 Reserved

15:17

SysCkRatio: PClock to SClock divisor, frequency relationship between

SClock, RClock, and TClock and PClock, bit 17 most significant

0 Divide by 2

1 Divide by 3

2 Divide by 4

3 Divide by 6 (R4400 processor only)

4 Divide by 8 (R4400 processor only)

5-7 Reserved

18 SIMasterMd: Master/Checker Mode (see mode bit 42); used in R4400 only.

19

TimIntDis: Timer Interrupt enable allows timer interrupts, otherwise the

interrupt used by the timer becomes a general purpose interrupt

0 Timer Interrupt enabled

1 Timer Interrupt disabled

20

PotUpdDis: Potential update enable allows potential updates to be issued.

Otherwise, only compulsory updates are issued

0 Potential updates enabled

1 Potential updates disabled

21:24

TWrSUp: Secondary cache write deassertion delay, T

WrSup

in PCycles, bit

24 most significant

0-2 Undefined

3-15 Number of PClock cycles: Min 3, Max 15

Loading...

Loading...