Chapter 9

224 MIPS R4000 Microprocessor User's Manual

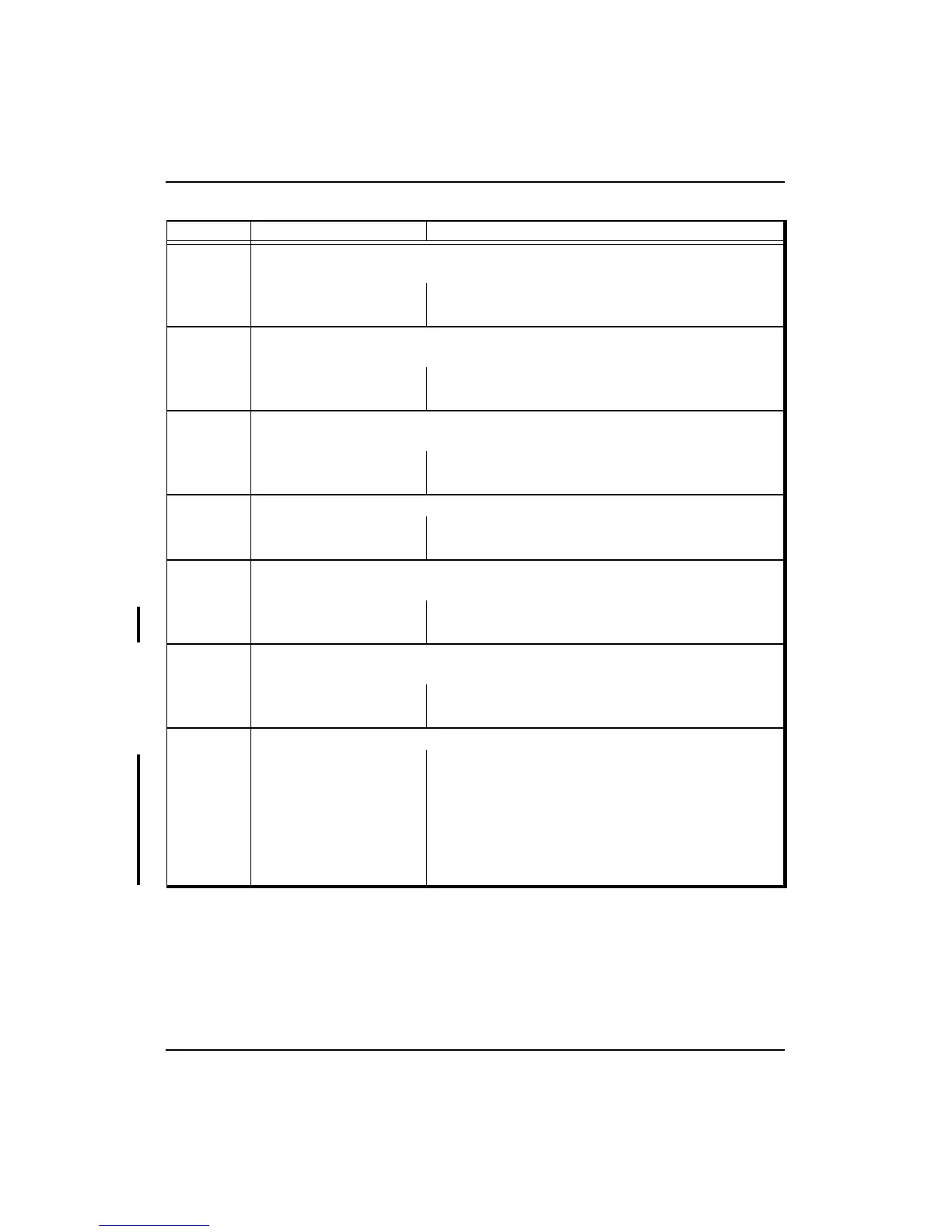

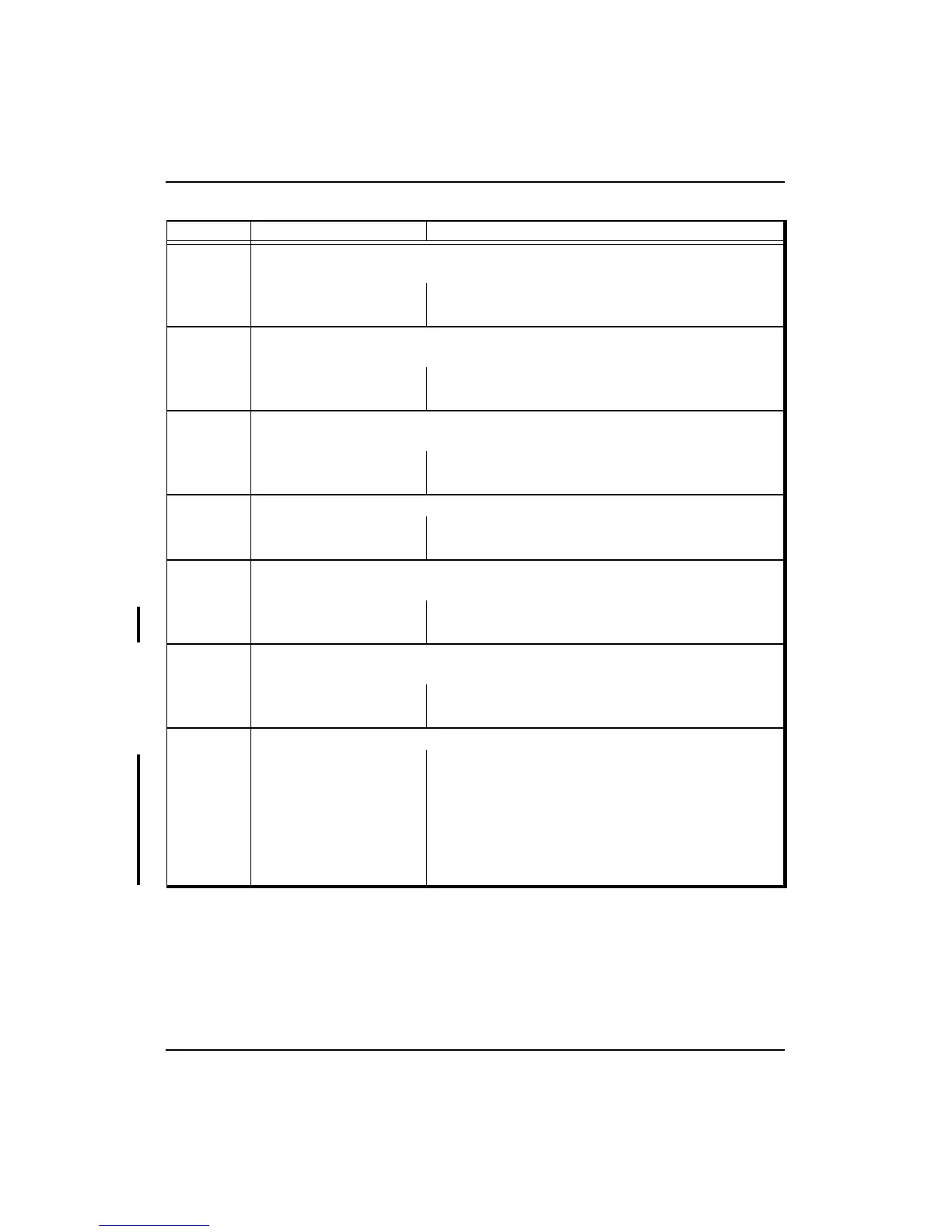

Table 9-1 (cont.) Boot-Mode Settings

Serial Bit Value Mode Setting

25:26

TWr2Dly: Secondary cache write assertion delay 2, T

Wr2Dly

in PCycles, bit

26 most significant

0

1-3

Undefined

Number of PClock cycles: Min 1, Max 3

27:28

TWr1Dly: Secondary cache write assertion delay 1, T

Wr1Dly

in PCycles, bit

28 most significant

0

1-3

Undefined

Number of PClock cycles; Min 1, Max 3

29

TWrRc: Secondary cache write recovery time, T

WrRc

in PCycles, either 0 or

1 cycle

0

1

0 cycle

1 cycle

30:32

TDis: Secondary cache disable time, T

Dis

in PCycles, bit 32 most significant

0-1

2-7

Undefined

Number of PClock cycles: Min 2, Max 7

33:36

TRd2Cyc: Secondary cache read cycle time 2, T

RdCyc2

in PCycles, bit 36 most

significant

0-1

2-15

Undefined

Number of PClock cycles: Min 2, Max 15

37:40

TRd1Cyc: Secondary cache read cycle time 1, T

RdCyc1

in PCycles, bit 40 most

significant

0-3

4-15

Undefined

Number of PClock cycles: Min 4, Max 15

41

NoMPmode: Secondary cache line is not invalidated

0

NoMPmode off: after a secondary cache miss, the

existing valid cache line is invalidated (following

writeback if necessary)

1

NoMPmode on: after a secondary cache miss, the

existing valid cache line is not invalidated.

Available on the R4000SC and R4400SC, to

improve performance.

Loading...

Loading...