MIPS R4000 Microprocessor User's Manual 225

Initialization Interface

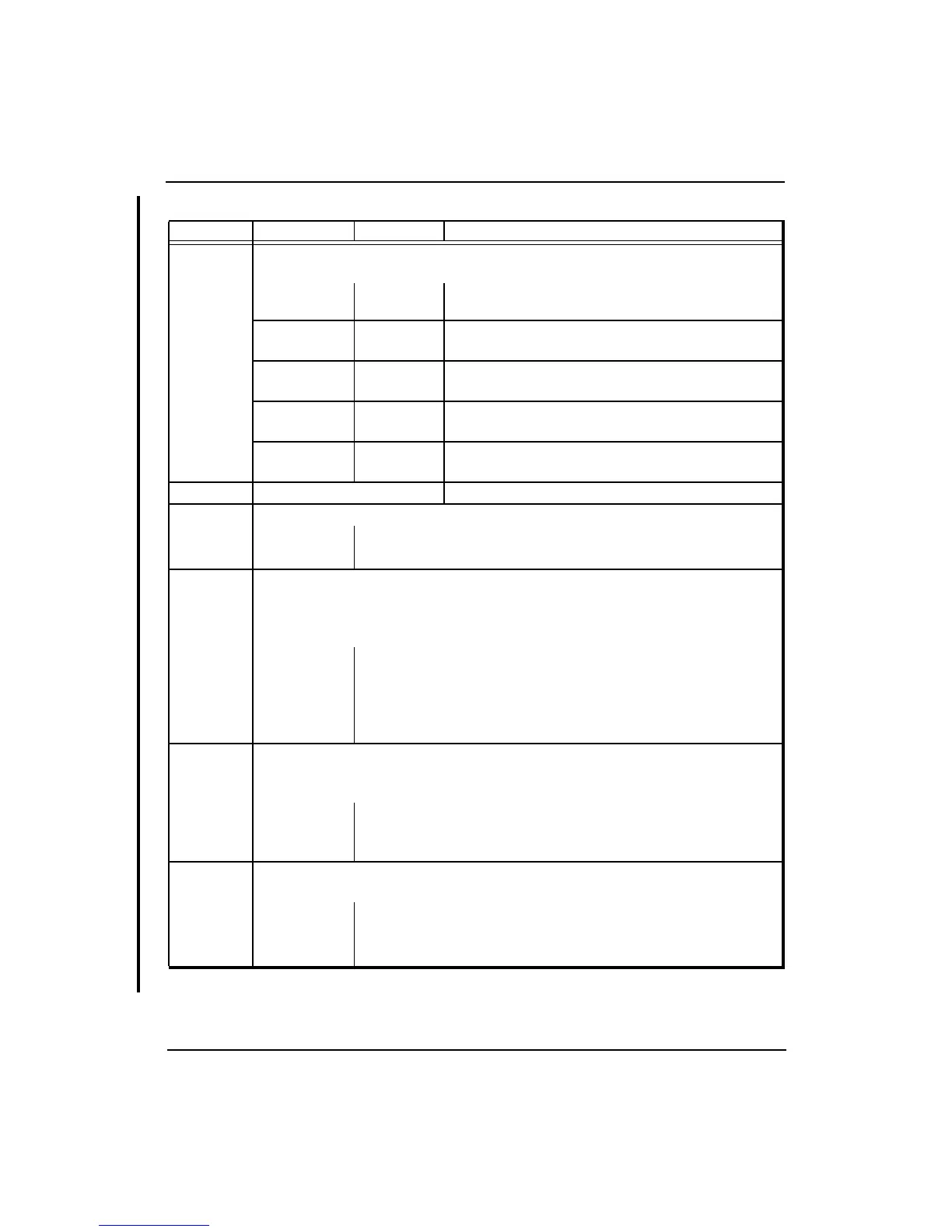

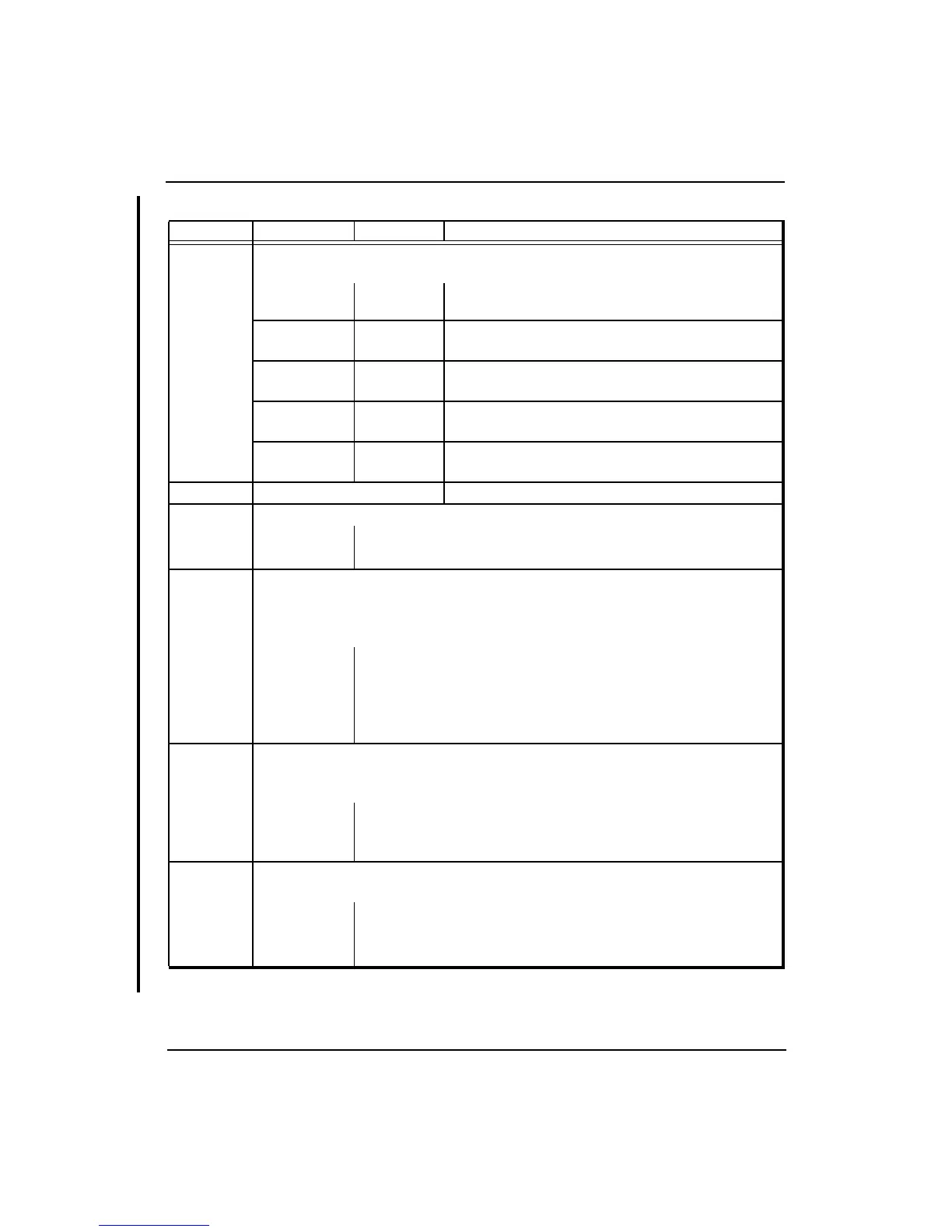

Table 9-1 (cont.) Boot-Mode Settings

Serial Bit Value Mode Setting

42

SCMasterMd: selects the type of Master/Checker mode (also see

description of mode bit 18). Used in R4400 only.

SCMasterMd

(Bit 42)

SIMasterMd

(Bit 18)

Mode

00

Complete Master

(required for single-chip operation)

11

Complete Listener

(paired with Complete Master)

10

System Interface Master

(SIMaster)

01

Secondary Cache Master

(SCMaster, paired with SIMaster)

43:45 0 Reserved

46

Pkg179: R4000 Processor Package type

0 Large (447 pin)

1 Small (179 pin)

47:49

CycDivisor: This mode determines the clock divisor for the reduced

power mode. When the RP bit in the Status register is set to 1, the pipeline

clock is divided by one of the following values. Bit 49 is the most

significant.

0

1

2

3

4-7

Divide by 2

Divide by 4

Divide by 8

Divide by 16

Reserved

50:52

Drv0_50, Drv0_75, Drv1_00: Drive the outputs out in n x MasterClock

period. Bit 52 is the most significant. Combinations not defined below are

reserved.

1

2

4

Drive at 0.50 x MasterClock period

Drive at 0.75 x MasterClock period

Drive at 1.00 x MasterClock period

53:56

InitP: Initial values for the state bits that determine the pull-down ∆i/∆t

and switching speed of the output buffers. Bit 53 is the most significant.

0

1-14

15

Fastest pull-down rate

Intermediate pull-down rates

Slowest pull-down rate

Loading...

Loading...