Chapter 9

226 MIPS R4000 Microprocessor User's Manual

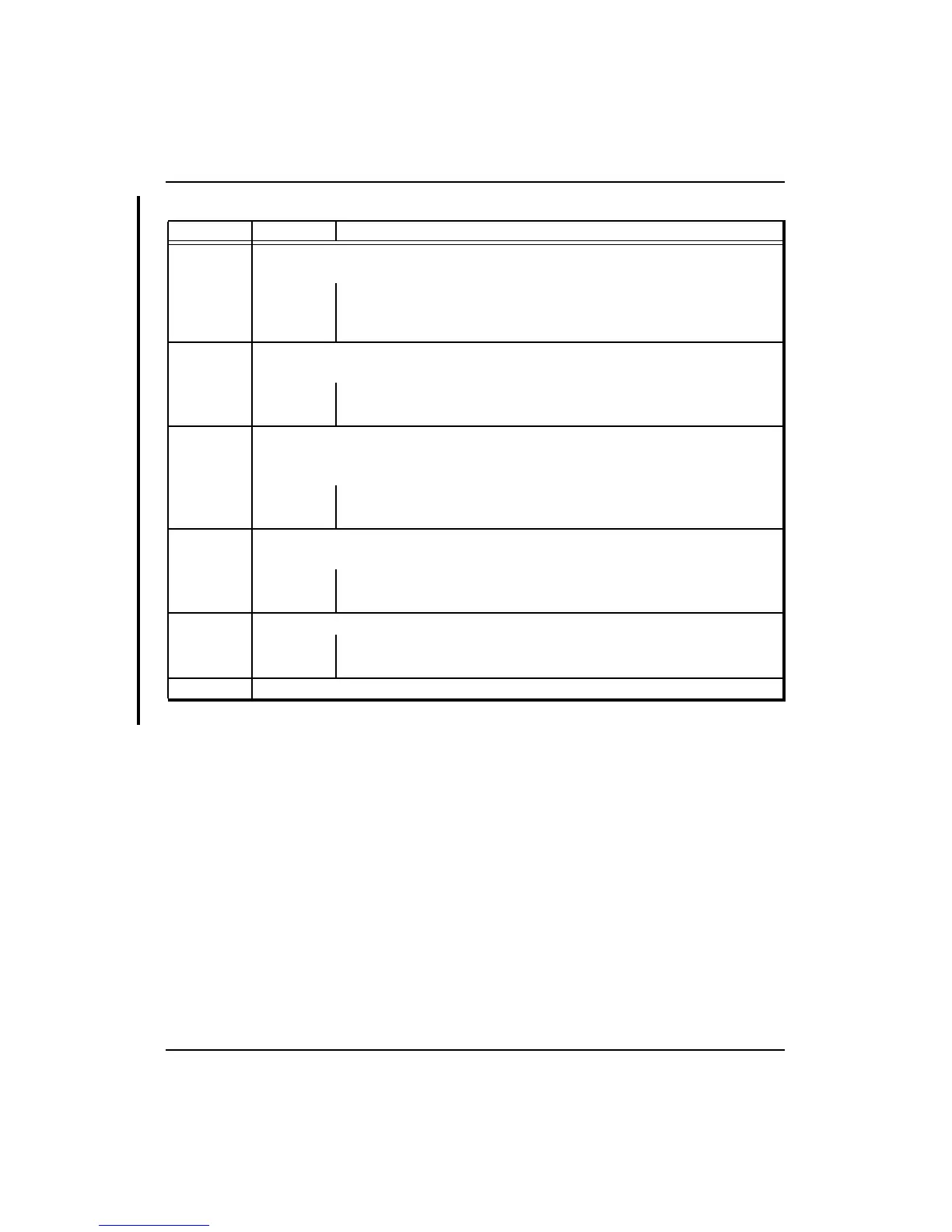

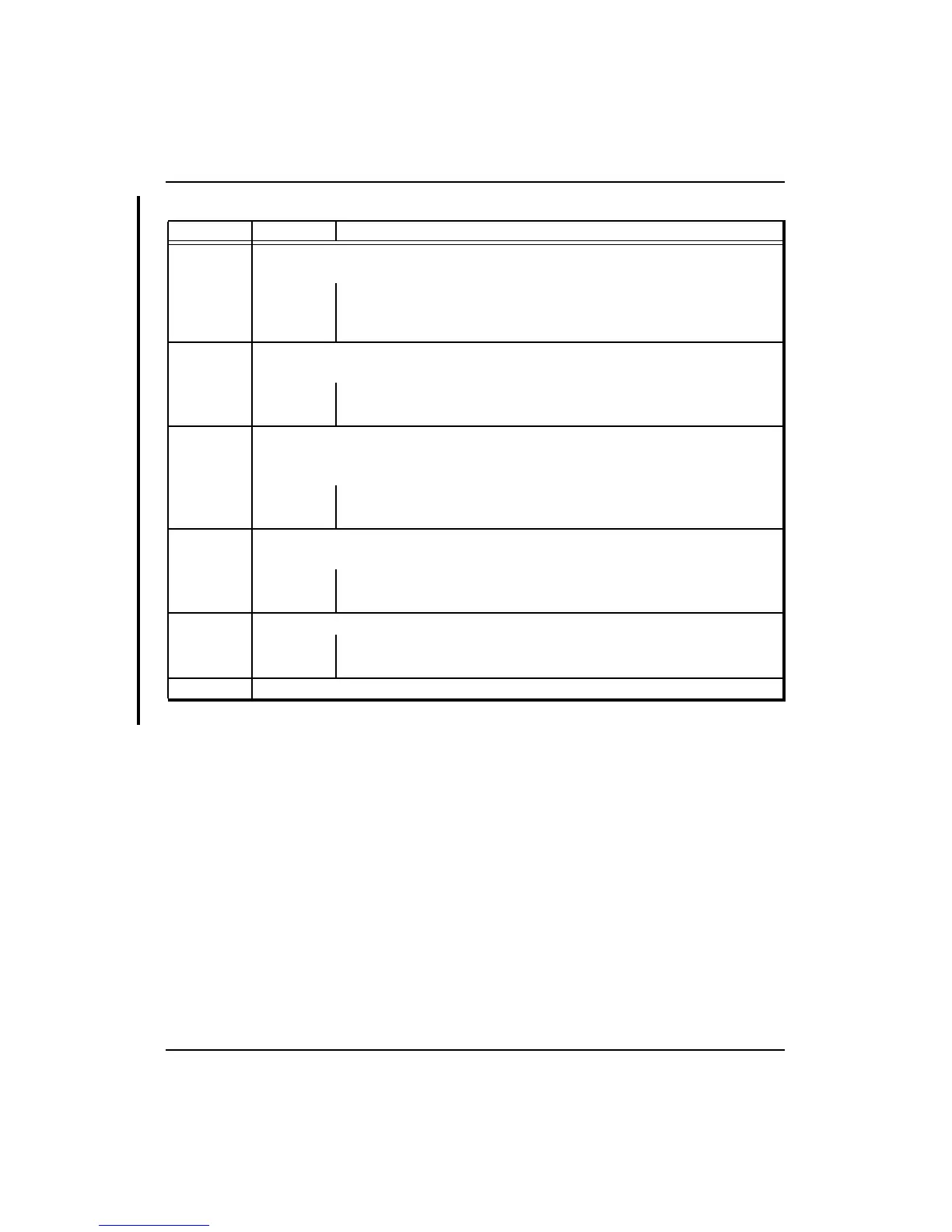

Table 9-1 (cont.) Boot-Mode Settings

Serial Bit Value Mode Setting

57:60

InitN: Initial values for the state bits that determine the pull-up ∆i/∆t and

switching speed of the output buffers. Bit 57 is the most significant.

0

1-14

15

Slowest pull-up rate

Intermediate pull-up rates

Fastest pull-up rate

61

EnblDPLLR: Enables the negative feedback loop that determines the

∆i/∆t and switching speed of the output buffers during ColdReset.

0

1

Disable ∆i/∆t mechanism

Enable ∆i/∆t mechanism

62

EnblDPLL: Enables the negative feedback loop that determines the ∆i/∆t

and switching speed of the output buffers during ColdReset and during

normal operation.

0

1

Disable ∆i/∆t control mechanism

Enable ∆i/∆t control mechanism

63

DsblPLL: Disables the phase-locked loops (PLLs) that match MasterClock

and produce RClock, TClock, SClock, and the internal clocks.

0

1

Enable PLLs

Disable PLLs

64

SRTristate: Controls when output-only pins are tristated

0 Only when ColdReset* is asserted

1 When Reset* or ColdReset* are asserted

65:255 Reserved. Scan in zeros.

Loading...

Loading...