MIPS R4000 Microprocessor User's Manual 351

System Interface

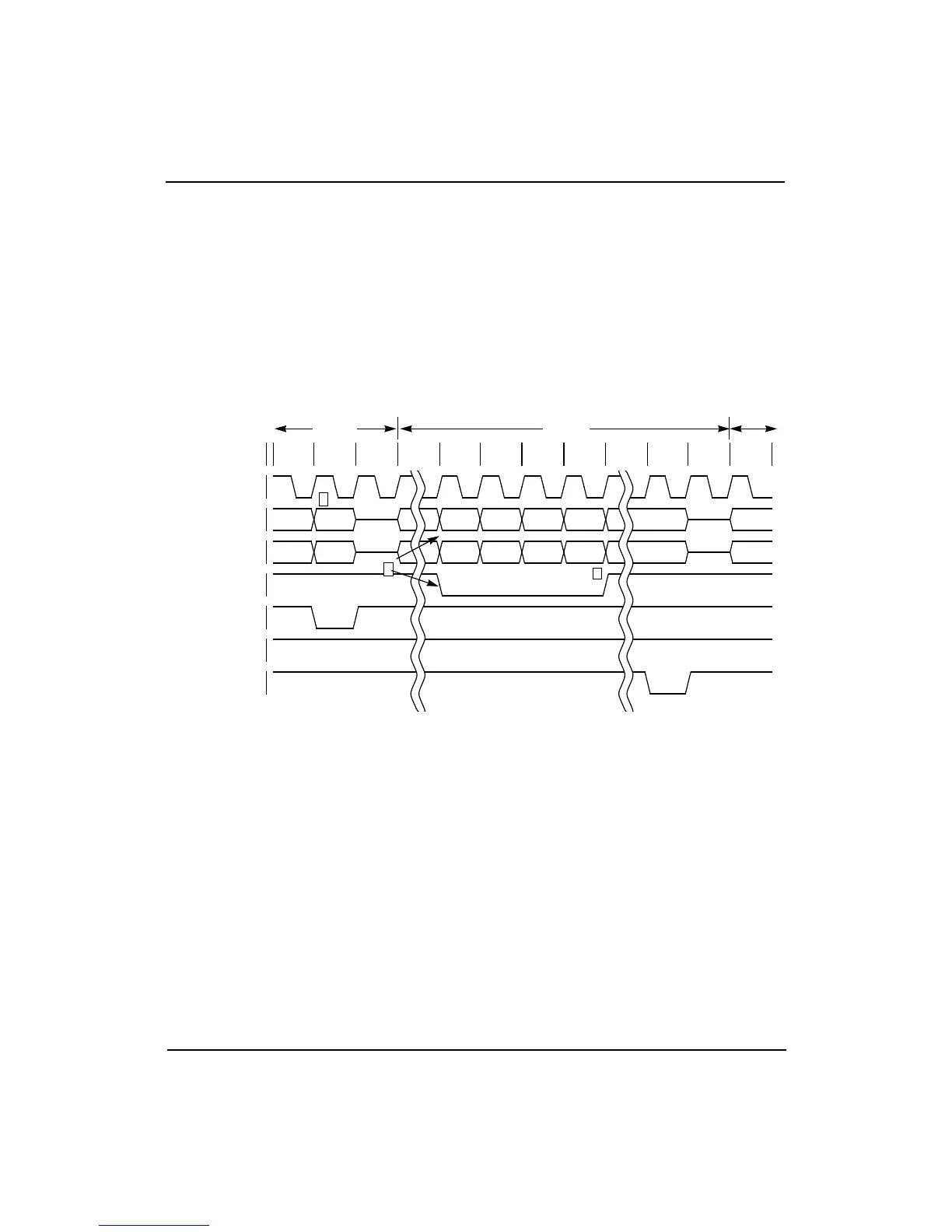

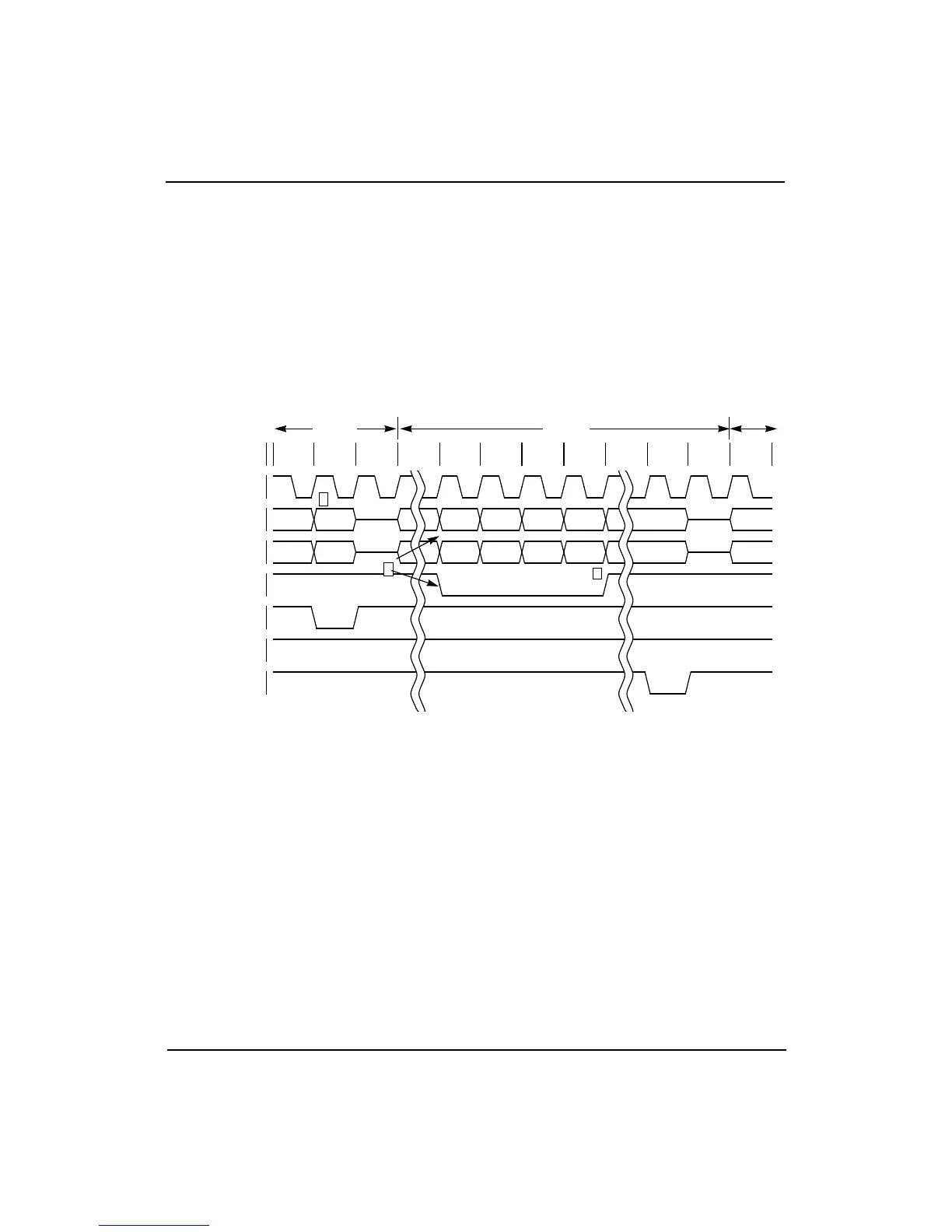

The case in which the processor returns cache line contents is described in

the steps below. In this example, the system is already in slave state.

1. The external intervention request is driven onto the SysCmd bus and

the address onto the SysAD bus. ValidIn* is asserted for one cycle.

2. The processor drives data on the SysAD bus and a data identifier on

the SysCmd bus. The processor asserts ValidOut* for each data cycle.

3. The data identifier associated with the last data cycle must contain a

last data cycle indicator.

Figure 12-35 External Intervention Request, Dirty Exclusive Line, System Interface in Slave State

The processor returns the contents of a cache line, along with an indication

of the cache state in which it was found, by issuing a sequence of data

cycles sufficient to transmit the contents of the cache line, as shown in

Figure 12-35. The data identifier transmitted with each data cycle

indicates the cache state in which the cache line was found, together with

an indication that this data is response data. The data identifier associated

with the last data cycle contains a last data cycle indication.

If the contents of a cache line are returned in response to an intervention

request, they are returned in subblock order starting with the doubleword

at the address supplied with the intervention request. Note, however, that

if the intervention address targets the doubleword at the beginning of the

block, subblock ordering is equivalent to sequential ordering.

SCycle

1 2 3 4 5 6 7 8 9 10 11 12

SClock

SysAD Bus

Addr Data0 Data1 Data2 Data3

SysCmd Bus

Ivtn CData CData CData CEOD

ValidOut*

ValidIn*

ExtRqst*

Release*

3

2

Slave

Master

Slave

1

Loading...

Loading...