Chapter 15

406 MIPS R4000 Microprocessor User's Manual

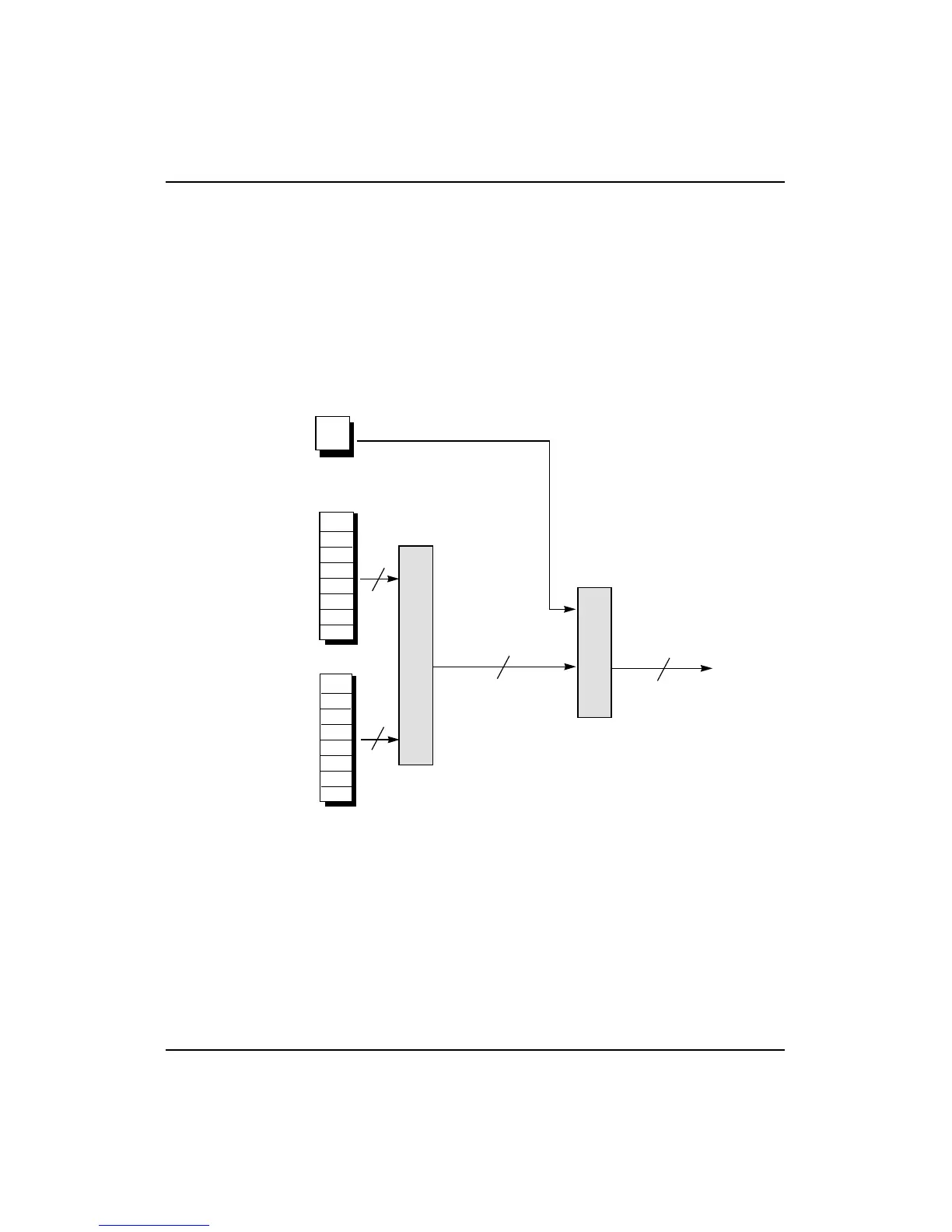

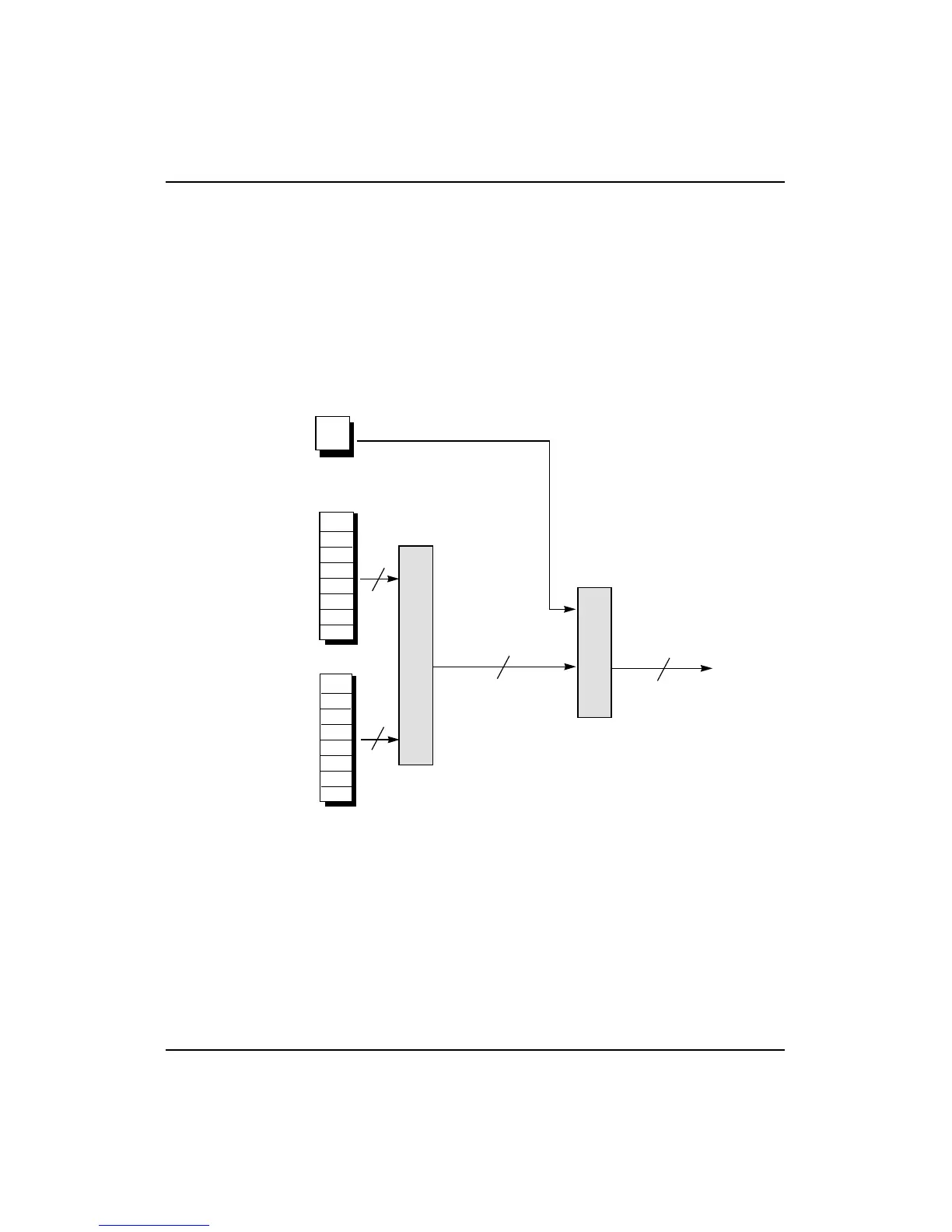

Figure 15-5 shows the masking of the R4000 interrupt signal.

• Cause register bits 15:8 (IP7-IP0) are AND-ORed with Status

register interrupt mask bits 15:8 (IM7-IM0) to mask individual

interrupts.

• Status register bit 0 is a global Interrupt Enable (IE). It is

ANDed with the output of the AND-OR logic to produce the

R4000 interrupt signal.

Figure 15-5 Masking of the R4000 Interrupt

Status register

SR(15:8)

AND-OR

function

IM2

IM1

IM0

IM4

IM3

IM5

IM6

IM7

Cause register

(15:8)

IP2

IP1

IP0

IP4

IP3

IP5

IP6

IP7

AND

function

R4000 Interrupt

IE

Status register

SR(0)

1

8

8

1

Loading...

Loading...