MIPS R4000 Microprocessor User's Manual 405

R4000 Processor Interrupts

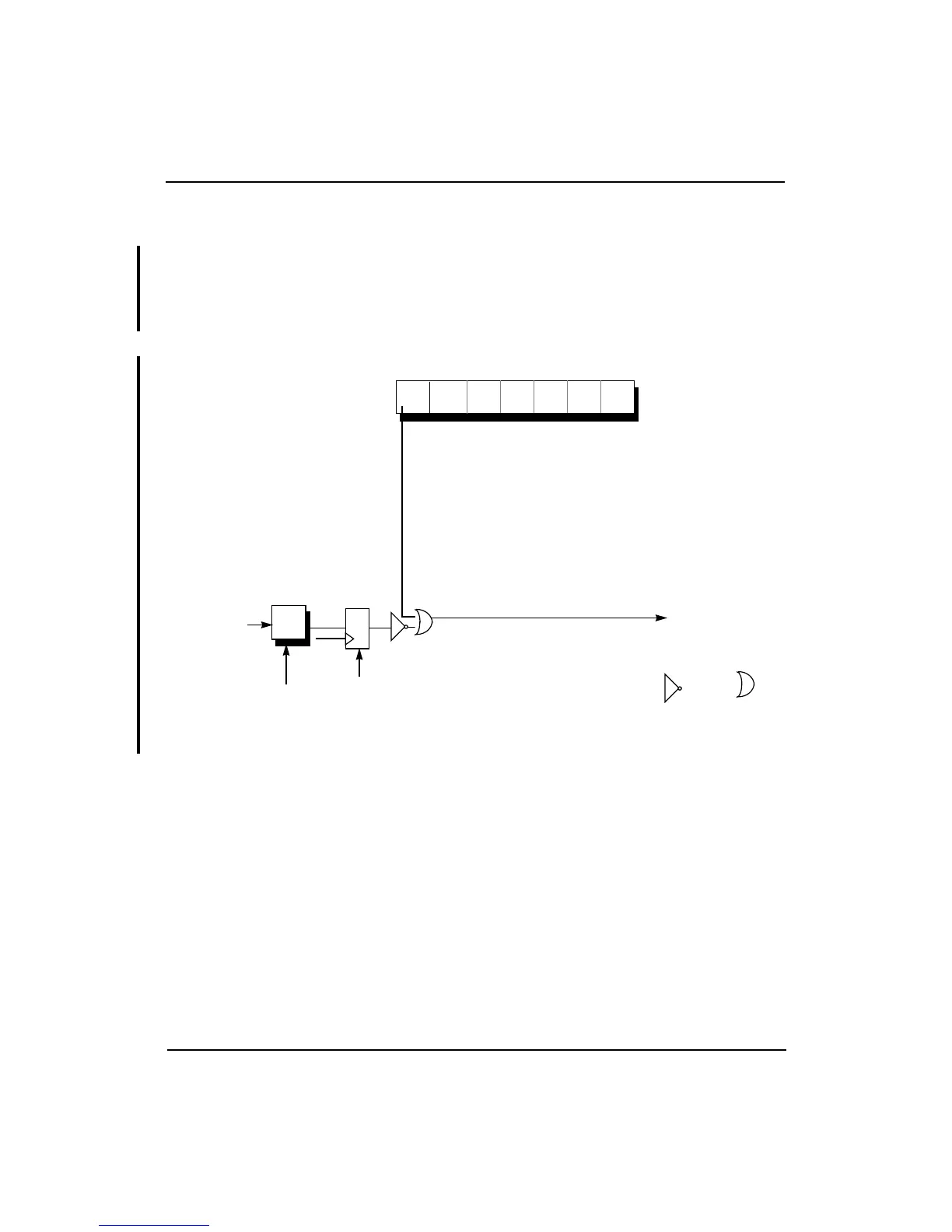

Figure 15-4 shows the internal derivation of the NMI signal, for all

versions of the R4000 processor.

The NMI* pin is latched by the rising edge of SClock, however the NMI

exception occurs in response to the falling edge of the NMI* signal, and is

not level-sensitive.

Bit 6 of the Interrupt register is then ORed with the inverted value of NMI*

to form the nonmaskable interrupt.

Figure 15-4 R4000 Nonmaskable Interrupt Signal

(Internal)

6

Interrupt register (6)

NMI*

OR gate

NMI

Inverter

SClock

(Internal

register)

Edge-

triggered

Flip-flop

Loading...

Loading...