MIPS R4000 Microprocessor User's Manual A-3

CPU Instruction Set Details

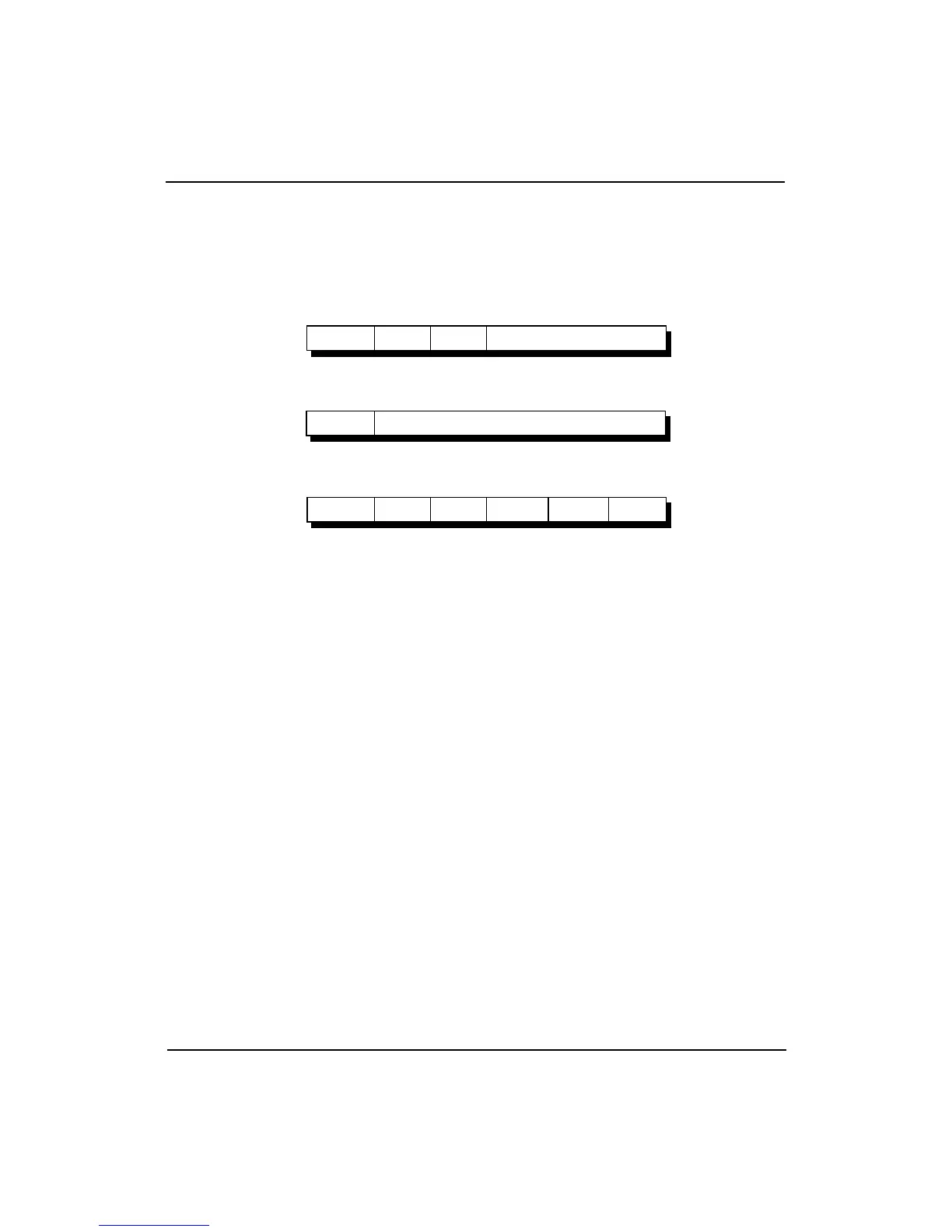

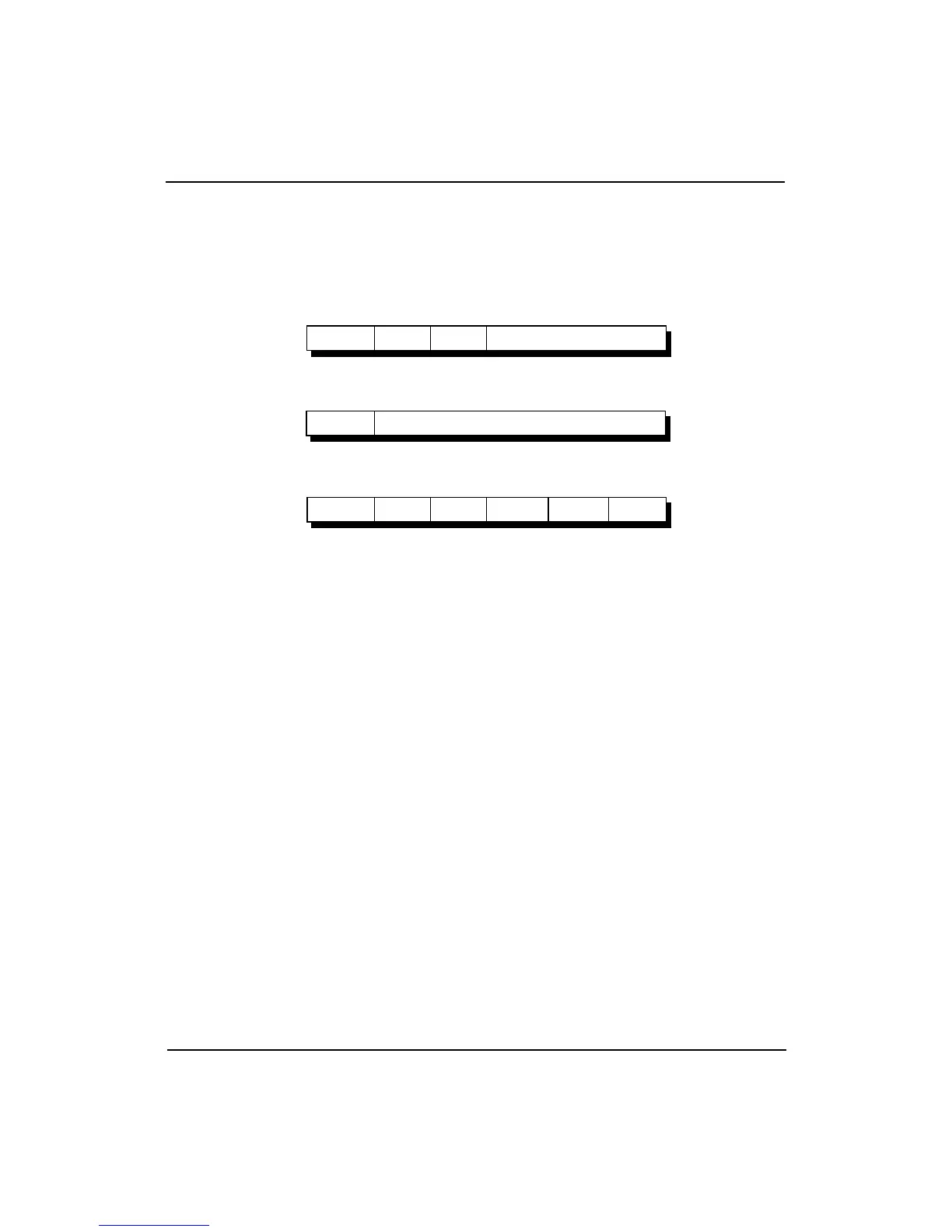

A.2 Instruction Formats

Every CPU instruction consists of a single word (32 bits) aligned on a word

boundary and the major instruction formats are shown in Figure A-1.

Figure A-1 CPU Instruction Formats

015162021252631

015162021252631

0252631

op

rs rt immediate

op target

funct

op

rs rt

1110

65

rd

shamt

R-Type (Register)

J-Type (Jump)

I-Type (Immediate)

op 6-bit operation code

rs 5-bit source register specifier

rt 5-bit target (source/destination) or branch condition

immediate

16-bit immediate, branch displacement or address

displacement

target 26-bit jump target address

rd 5-bit destination register specifier

shamt 5-bit shift amount

funct 6-bit function field

Loading...

Loading...