Appendix A

A-12 MIPS R4000 Microprocessor User's Manual

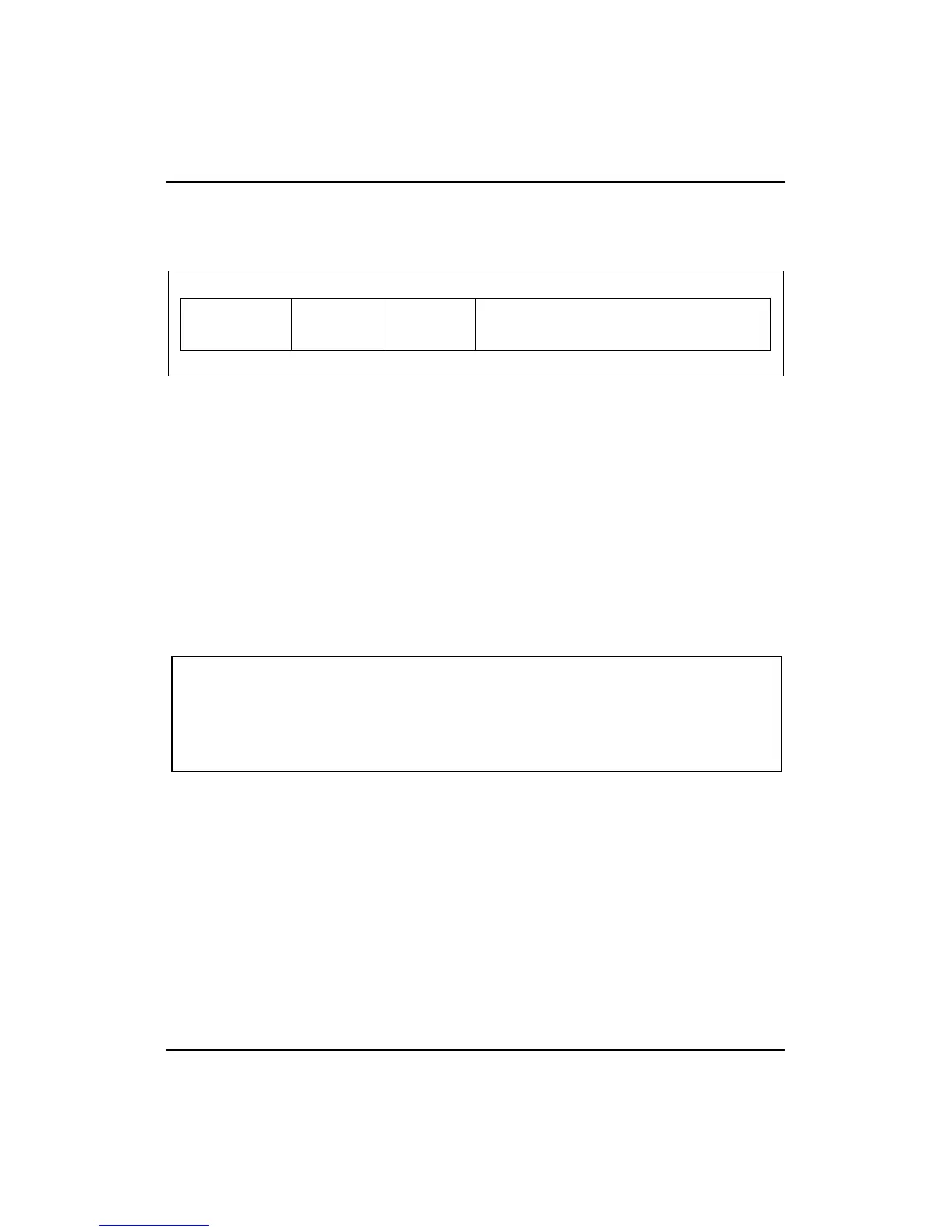

Format:

ADDI rt, rs, immediate

Description:

The 16-bit immediate is sign-extended and added to the contents of general

register rs to form the result. The result is placed into general register rt.

In 64-bit mode, the operand must be valid sign-extended, 32-bit values.

An overflow exception occurs if carries out of bits 30 and 31 differ (2’s

complement overflow). The destination register rt is not modified when

an integer overflow exception occurs.

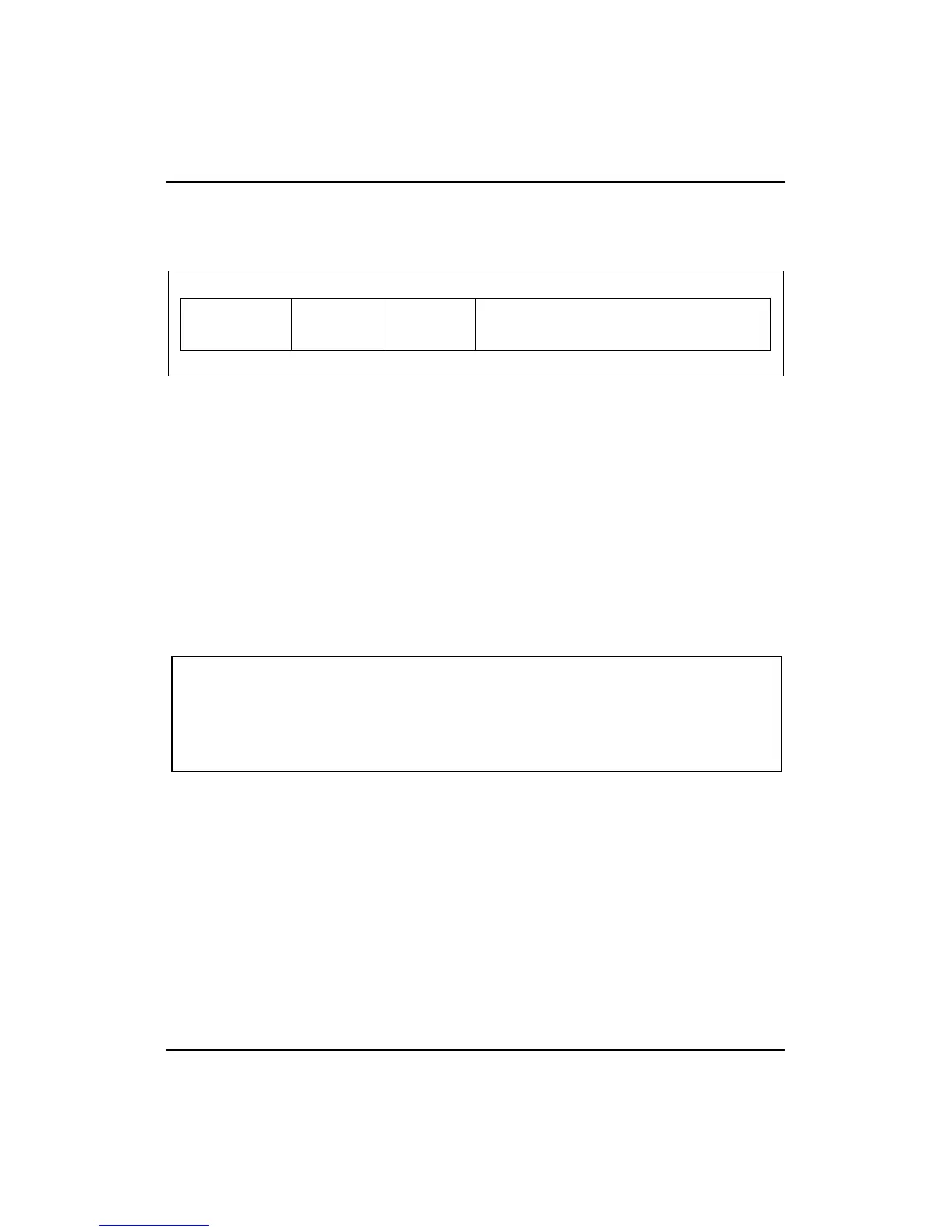

Operation:

Exceptions:

Integer overflow exception

ADDI

Add Immediate

31 2526 2021 1516 0

ADDI

rs rt

immediate

655 16

0 0 1 0 0 0

ADDI

32 T: GPR [rt] ← GPR[rs] +(immediate

15

)

16

|| immediate

15...0

64 T: temp ← GPR[rs] + (immediate

15

)

48

|| immediate

15...0

GPR[rt] ← (temp

31

)

32

|| temp

31...0

Loading...

Loading...