Appendix A

A-48 MIPS R4000 Microprocessor User's Manual

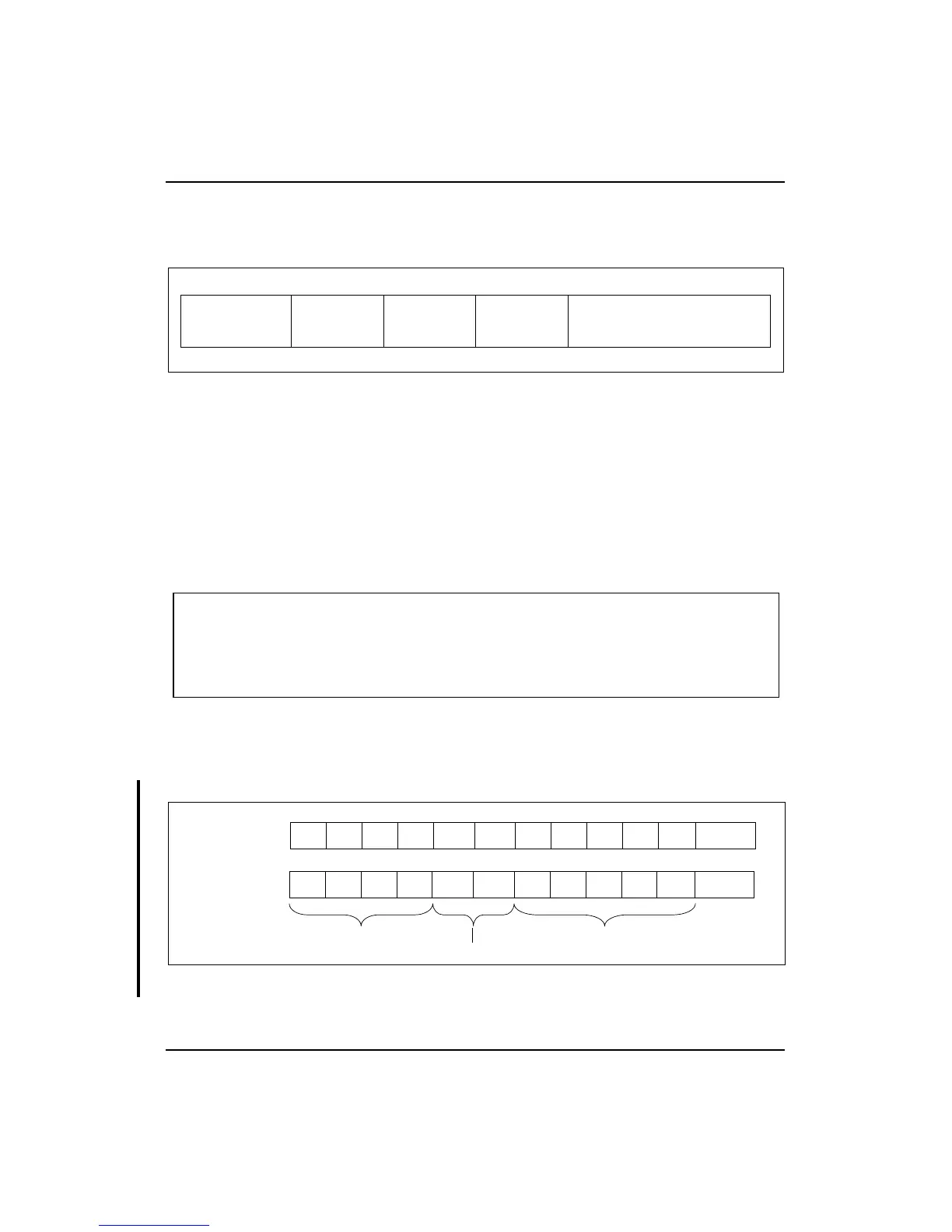

Format:

CFCz rt, rd

Description:

The contents of coprocessor control register rd of coprocessor unit z are

loaded into general register rt.

This instruction is not valid for CP0.

Operation:

Exceptions:

Coprocessor unusable exception

*Opcode Bit Encoding:

Coprocessor

CFCz

11

Move Control From

31 2526 2021 1516

COPz CF rt

655

rd

0

5

11 10 0

0 1 0 0 x x* 0 0 0 1 0 0 0 0 0 0

CFCz

32 T: data ← CCR[z,rd]

T+1: GPR[rt] ← data

64 T: data ← (CCR[z,rd]

31

)

32

|| CCR[z,rd]

T+1: GPR[rt] ← data

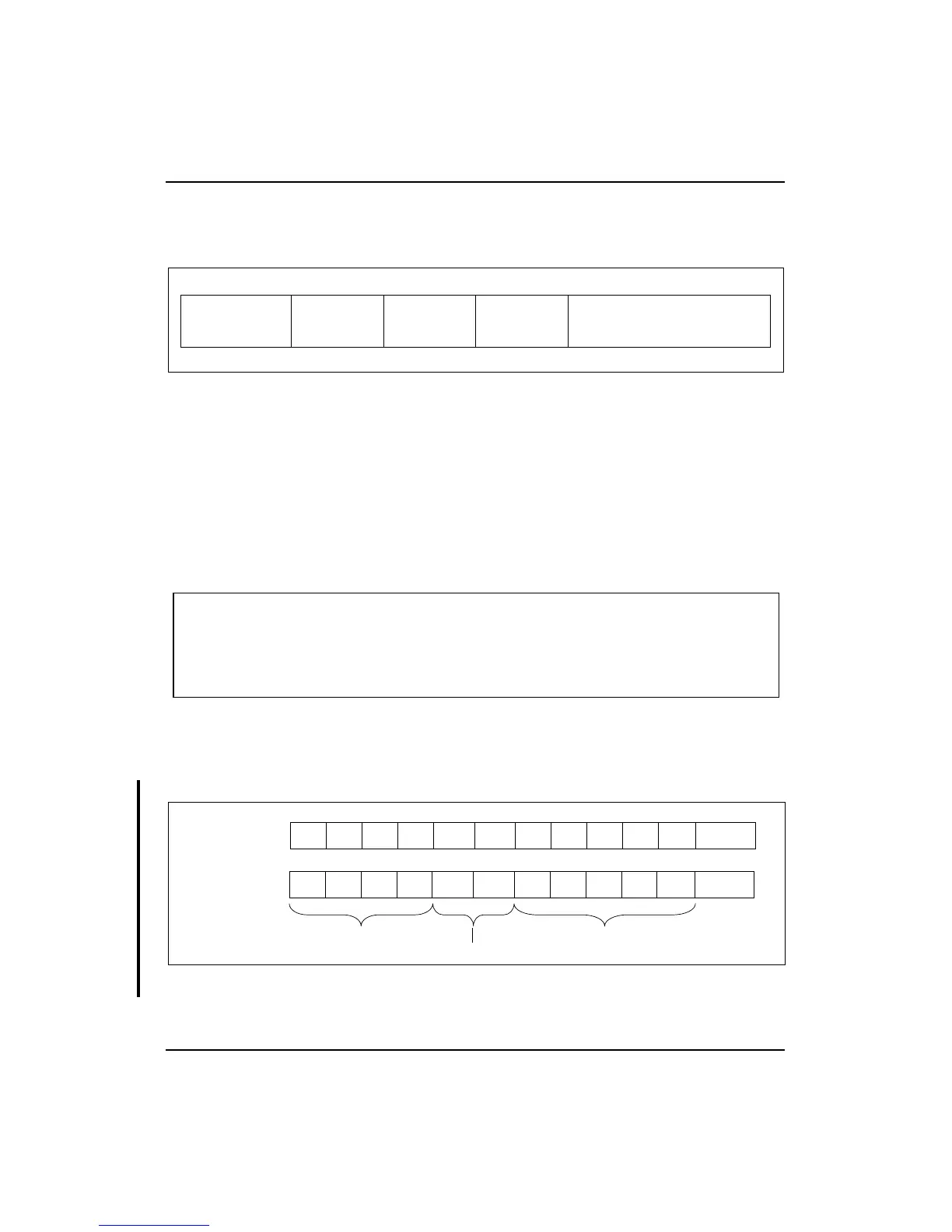

CFCz

000011

31 30 29 28 27 26

Bit #

25 0

CFC1

00100

24 23 22

21

000101

31 30 29 28 27 26

Bit #

25 0

CFC2

00100

24 23 22

21

Coprocessor Unit Number

Coprocessor SuboperationOpcode

Loading...

Loading...