MIPS R4000 Microprocessor User's Manual A-53

CPU Instruction Set Details

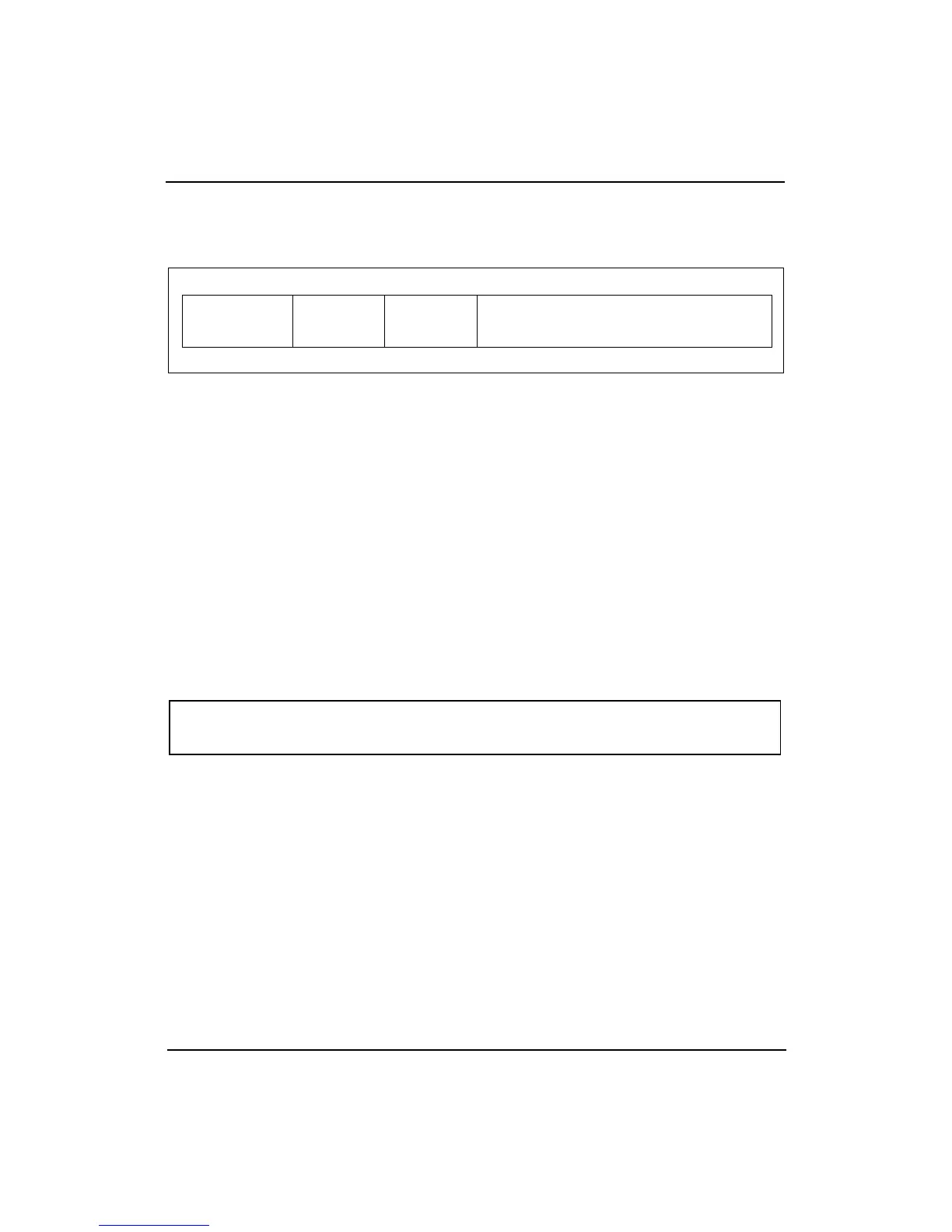

Format:

DADDIU rt, rs, immediate

Description:

The 16-bit immediate is sign-extended and added to the contents of general

register rs to form the result. The result is placed into general register rt.

No integer overflow exception occurs under any circumstances.

The only difference between this instruction and the DADDI instruction is

that DADDIU never causes an overflow exception.

This operation is only defined for the R4000 operating in 64-bit mode.

Execution of this instruction in 32-bit mode causes a reserved instruction

exception.

Operation:

Exceptions:

Reserved instruction exception (R4000 in 32-bit mode)

DADDIU

Doubleword Add

31 2526 2021 1516 0

DADDIU

rs rt

immediate

655 16

0 1 1 0 0 1

DADDIU

Immediate Unsigned

64 T: GPR [rt] ← GPR[rs] + (immediate

15

)

48

|| immediate

15...0

Loading...

Loading...