Appendix A

A-80 MIPS R4000 Microprocessor User's Manual

Format:

JR rs

Description:

The program unconditionally jumps to the address contained in general

register rs, with a delay of one instruction.

Since instructions must be word-aligned, a Jump Register instruction

must specify a target register (rs) whose two low-order bits are zero. If

these low-order bits are not zero, an address exception will occur when the

jump target instruction is subsequently fetched.

Operation:

Exceptions:

None

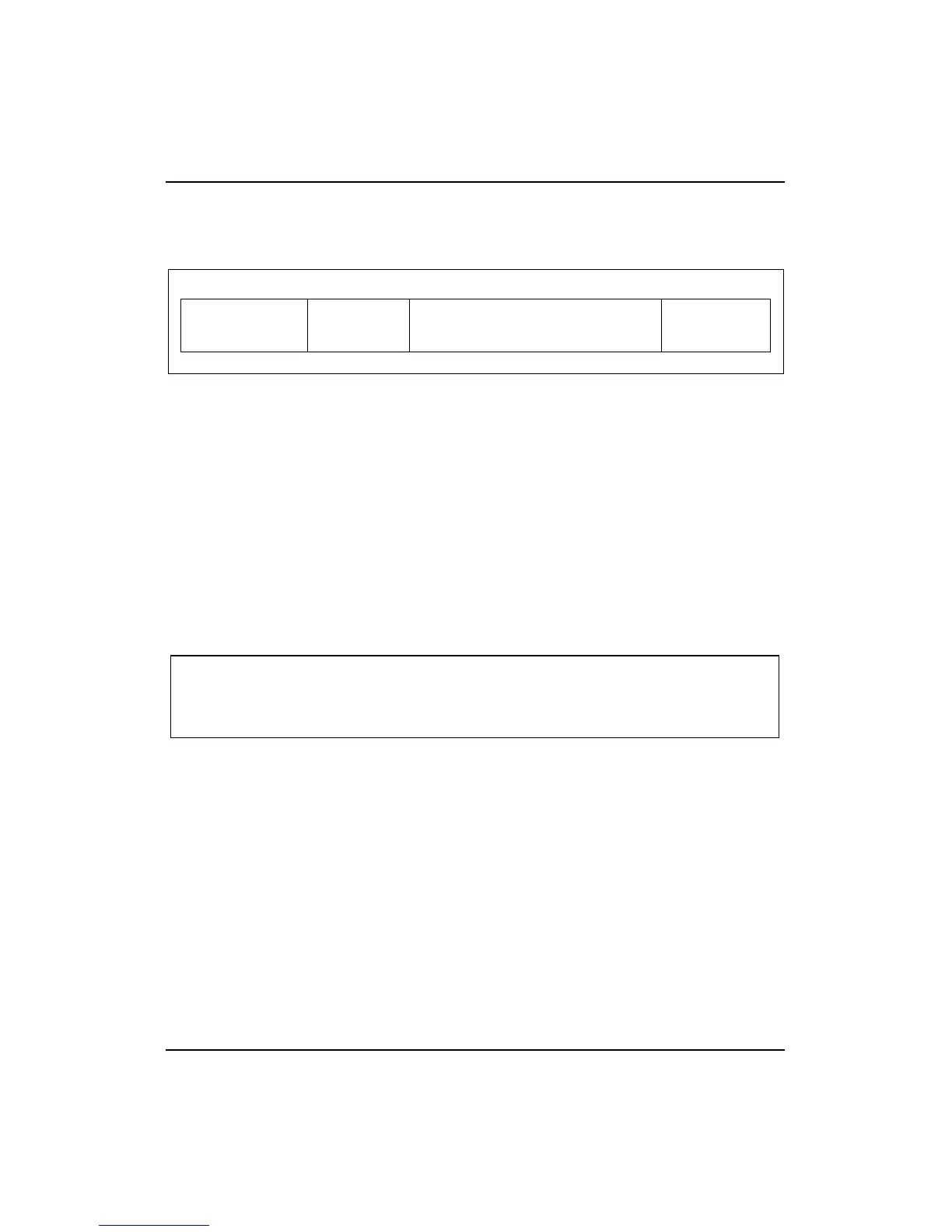

JR

Jump Register

21 2031 2526

SPECIAL

6

0

JRrs 0

6 5

515 6

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

JR

32, 64 T: temp ← GPR[rs]

T+1: PC ← temp

Loading...

Loading...