MIPS R4000 Microprocessor User's Manual A-79

CPU Instruction Set Details

Format:

JALR rs

JALR rd, rs

Description:

The program unconditionally jumps to the address contained in general

register rs, with a delay of one instruction. The address of the instruction

after the delay slot is placed in general register rd. The default value of rd,

if omitted in the assembly language instruction, is 31.

Register specifiers rs and rd may not be equal, because such an instruction

does not have the same effect when re-executed. However, an attempt to

execute this instruction is not trapped, and the result of executing such an

instruction is undefined.

Since instructions must be word-aligned, a Jump and Link Register

instruction must specify a target register (rs) whose two low-order bits are

zero. If these low-order bits are not zero, an address exception will occur

when the jump target instruction is subsequently fetched.

Operation:

Exceptions:

None

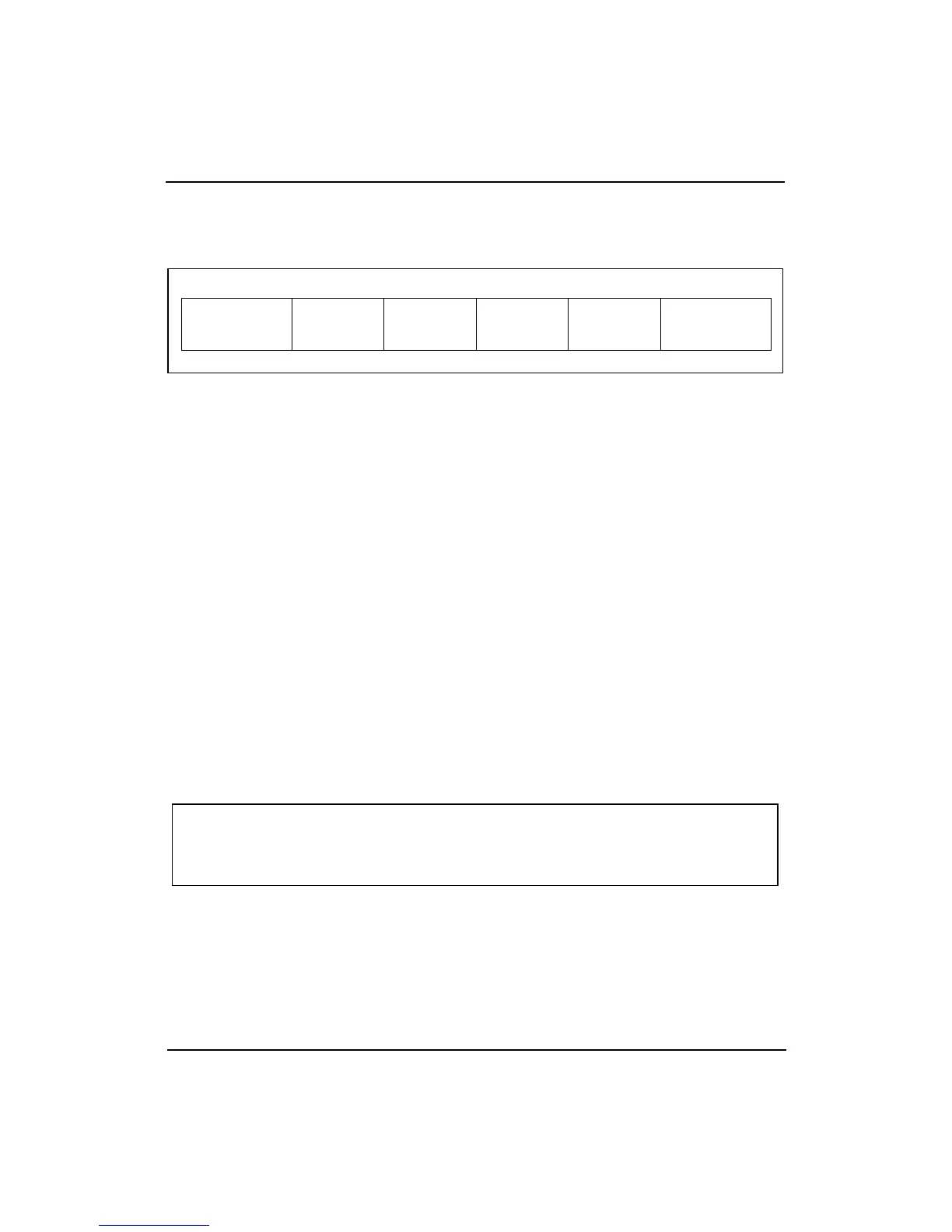

JALR

Jump And Link Register

31 2526 2021 1516

SPECIAL rs 0

655

rd 0 JALR

55 6

11 10 6 5 0

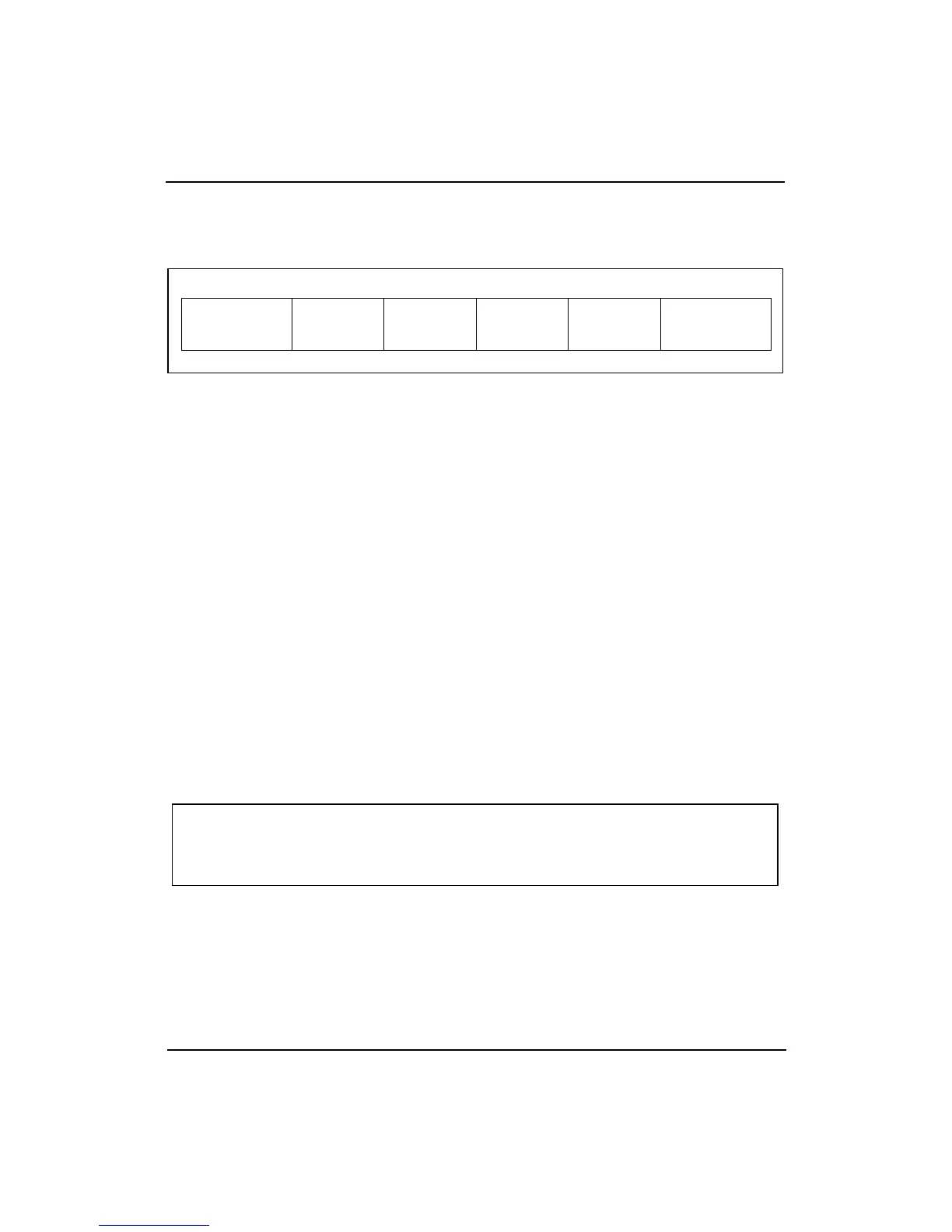

0 0 1 0 0 10 0 0 0 00 0 0 0 00 0 0 0 0 0

JALR

32, 64 T: temp ← GPR [rs]

GPR[rd] ← PC + 8

T+1: PC ← temp

Loading...

Loading...